Новиков А.А., Амелина М.А. Математическое моделирование в электронике. Курс лекций

Подождите немного. Документ загружается.

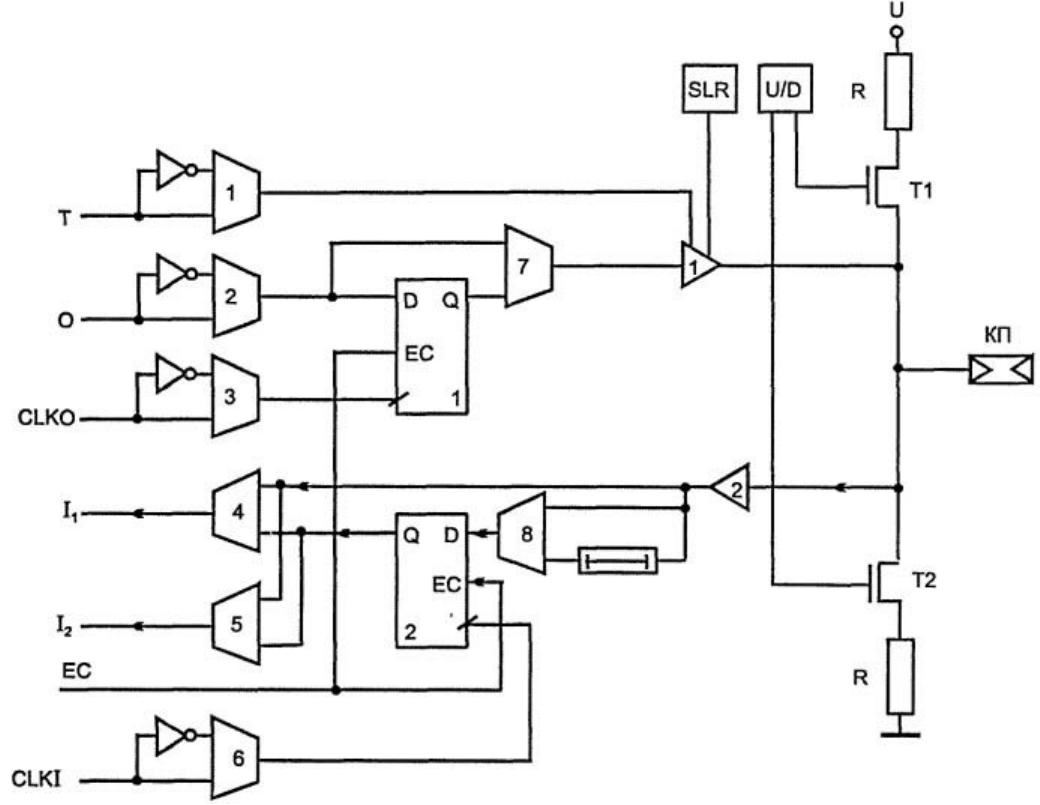

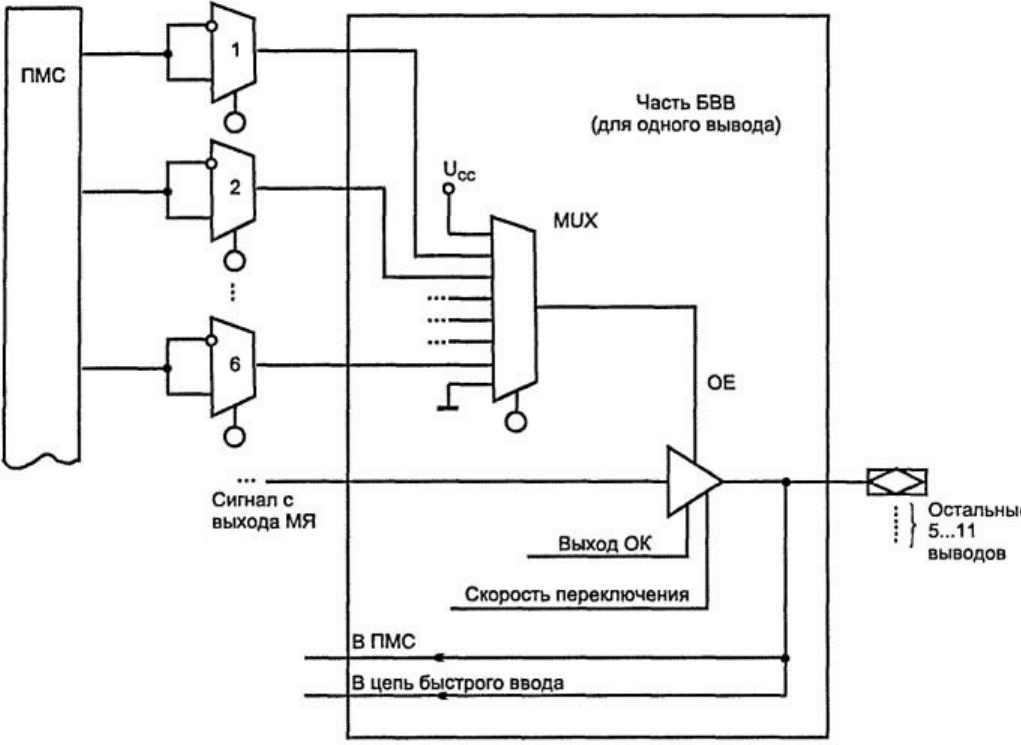

Рис. 8.8. Схема блока ввода/вывода FPGA семейства ХС4000Е

Благодаря резисторам R потенциал разомкнутой контактной площадки КП либо

"подтягивается" к высокому уровню, либо привязывается к нулевой точке. Выбор между

этими вариантами программируется элементами памяти конфигурации, имеющимися в

схеме U/D (Up/Down). Выходной буфер 1 имеет регулировку крутизны фронта (линия

SLR, Slew Rate). Скорости нарастания выходного сигнала можно придать одно из двух

значений (быстрая и медленная), для чего имеется программируемый элемент памяти в

схеме SLR. Пологие фронты снижают уровень помех, возникающих при работе схемы, и

желательны везде, где это приемлемо по соображениям быстродействия. При включении

питания во всех буферах устанавливается режим пологих фронтов.

403

Если внешний вывод работает в режиме входа (буфер 1 в третьем состоянии, буфер 2

активен), то внешний сигнал может подаваться в микросхему либо напрямую, либо через

триггер, либо в обоих вариантах одновременно. В последнем случае блок ввода/вывода

может демультиплексировать внешние сигналы (например, для шин адресов/данных

сохранять адрес в триггере и передавать данные по прямому входу). Синхросигналы

триггеров различны для входного (CLKI) и выходного (CLKO) триггера. Их полярности,

как и полярность выходного сигнала О (Output), могут программироваться

соответствующими мультиплексорами.

Сигнал на входе триггера 2 можно специально задерживать на несколько наносекунд

программированием мультиплексора 8. Это сделано для такого подбора временного

положения сигнала относительно тактирующего импульса, при котором обеспечивается

совместимость с шиной PCI.

Сложные программируемые логические схемы (CPLD) и СБИС программируемой

логики смешанной архитектуры (FLEX и др.)

Сложные программируемые логические ИС (СПЛИС) архитектурно произошли от

структур PLD (PAL, GAL) и называются CPLD (Complex Programmable Logic Deivices).

Для русского эквивалента этого названия примем СПЛИС, хотя в ряде работ встречается

наименование ПЛИС. Следовать этому нежелательно, т. к. многие авторы трактуют

термин ПЛИС как наименование всех ИС программируемой логики вообще. Приемлемым

вариантом названия для CPLD является и СПЛУ - сложные программируемые логические

устройства, что соответствует переводу термина CPLD на русский язык.

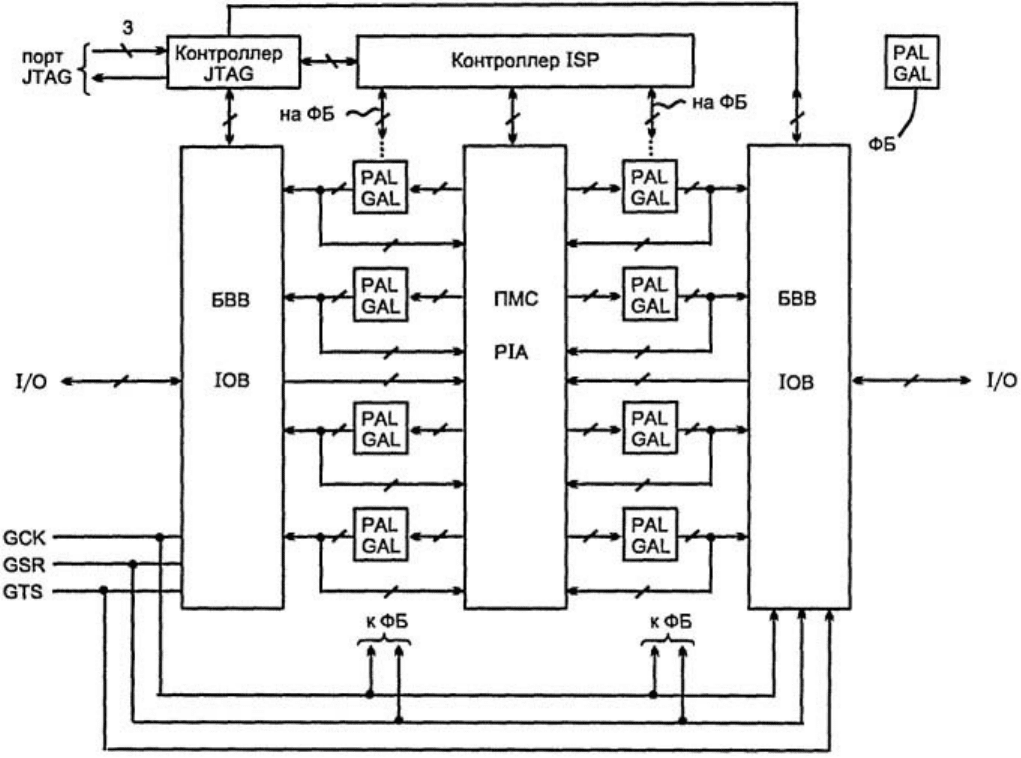

Архитектурно CPLD состоят из центральной коммутационной матрицы, множества

функциональных блоков ФБ (именуемых также макроячейками, макроэлементами и др.) и

блоков ввода/вывода на периферии кристалла. Архитектура CPLD показана на рис. 8.12,

где через ПМС обозначена программируемая матрица соединений (PIA, Programmable

Interconect Array).

412

Рис. 8.12. Архитектура CPLD

МИКРОСХЕМЫ ТИПА CPLD (НА ПРИМЕРЕ AlteraMAX 7000 )

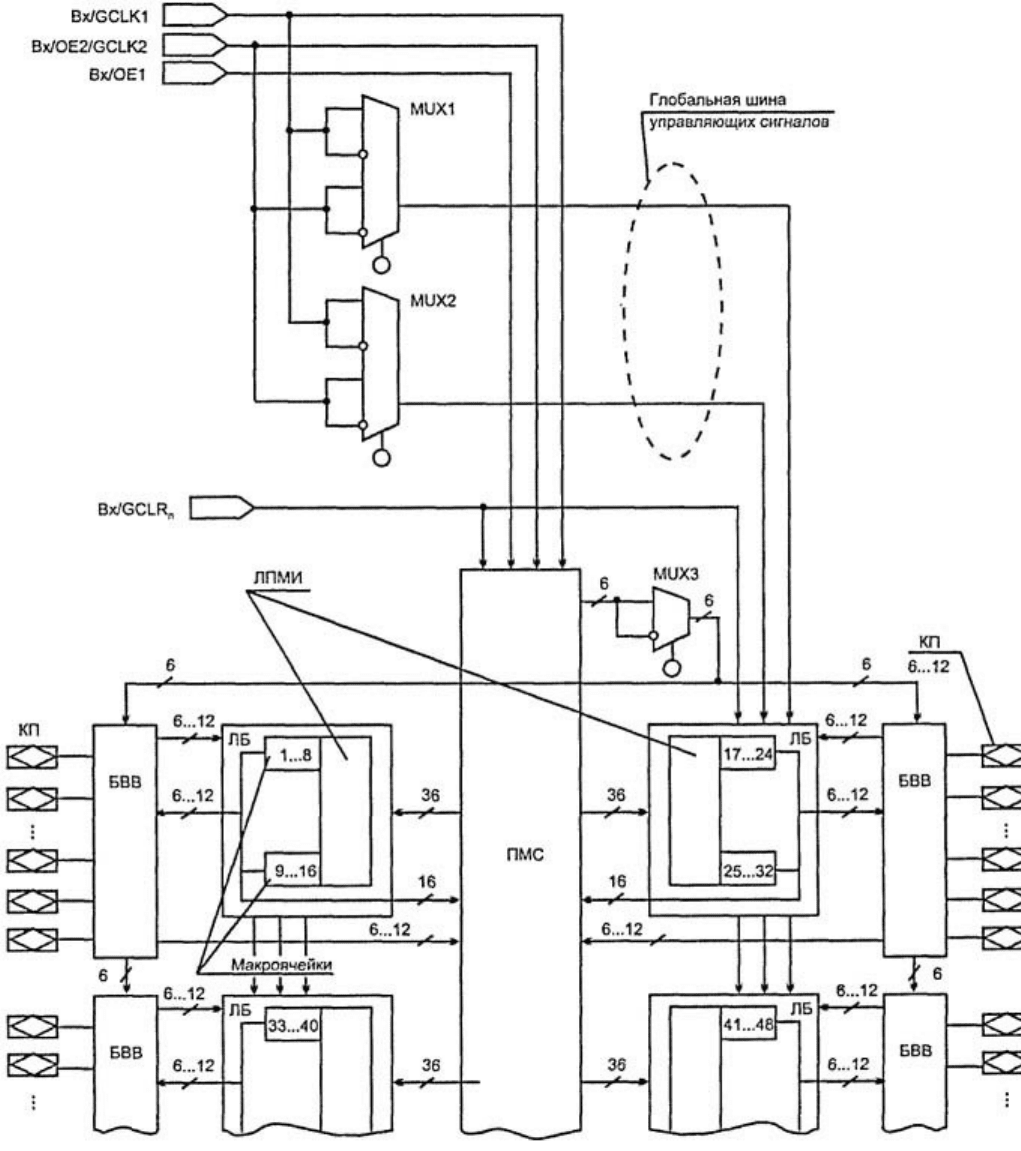

На рис. 8.14 показан фрагмент CPLD MAX 7000S, дающий достаточно полное

представление о ней, т. к. структура CPLD в целом составляется повторением

изображенного на фрагменте яруса из логических блоков ЛБ и блоков ввода/вывода БВВ

то или иное число раз (на рис. 8.14 повторяющиеся ярусы должны располагаться сверху

вниз) в зависимости от числа ЛБ у данной CPLD, т. е. от ее сложности. На рисунке

выделены логические блоки Л Б, содержащие по 16 макроячеек МЯ, получающих термы

от локальных программируемых матриц И (ЛПМИ), программируемая матрица

соединений ПМС и блоки ввода/вывода БВВ.

Микросхемы семейства МАХ 7000 имеют маркировку ЕРМ7ХХХ (усовершенствованные

варианты отмечаются дополнительной буквой в конце), где в трех последних позициях

размещается число МЯ у данной микросхемы (от 032 у младшего представителя до 256 у

старшего).

Как и во всех СБИС ПЛ, логические операции производятся в ЛБ, которые соединяются в

единую схему с помощью ПМС. Каждый Л Б содержит 16 макроячеек, так что у младшего

представителя семейства 2 логических блока, у старшего - 16.

ПМС обеспечивает возможность подачи на любой вход ЛБ сигнала от любого источника

(выходов ЛБ или контактов ввода/вывода), причем она организована так, что на пути

сигнала нет программируемых ключей, и задержки сигналов малы. Подача сигнала из

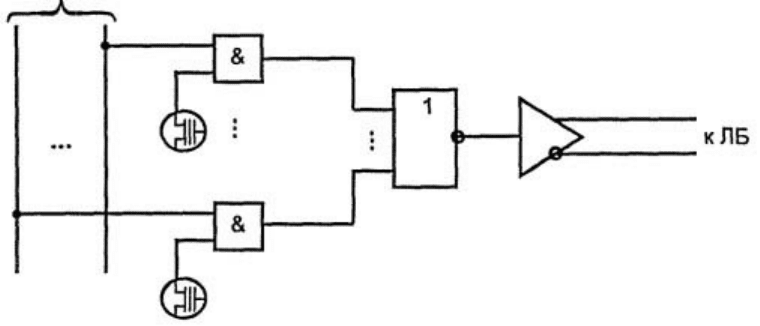

ПМС в ЛБ (рис. 8.15) происходит через конъюнктор, открытый по второму входу

единичным логическим сигналом с помощью программируемого транзистора, который не

находится в цепи передачи сигнала. На вход ЛБ можно передать сигнал с любой

вертикальной линии ПМС. Вертикальные линии непрерывны и идут по всей длине между

двумя столбцами из Л Б.

415

Рис. 8.14. Фрагмент структуры CPLD MAX 7000S

Каждый ЛБ непосредственно связан со своим блоком ввода/вывода, имеющим от 6 до 12

контактов (КП - контактная площадка). Как видно, не все макроячейки могут иметь

внешний вывод. Часть из них может быть использована только для подачи сигнала

обратной связи в ПМС, что является естественным при построении ряда узлов (счетчиков

и др.).

ПМС получает следующие сигналы: 16 сигналов обратной связи от каждого ЛБ, от 6 до 12

сигналов от БВВ, четыре сигнала (вверху на рис. 8.14)

416

от специализированных входов. Разное число контактов у БВВ позволяет выбирать более

экономичный вариант там, где требования интерфейса это допускают.

Рис. 8.15. Схема передачи сигналов из программируемой матрицы соединений в

логические блоки

К специализированным сигналам относятся так называемые глобальные сигналы

тактирования GCLK1 и GCLK2 и сброса GCLR, а также сигналы разрешения выходов ОЕ.

Здесь и в других случаях термин "глобальный" означает "единый для всех одноименных

блоков СБИС". При необходимости перечисленные линии могут быть использованы как

простые входы ПМС.

Из ПМС поступает по 36 сигналов для каждого Л Б и еще 6 сигналов, которые передаются

в прямом или инверсном виде через мультиплексор MUX3 для глобальной шины

разрешения выходов блока ввода/вывода.

Логический блок обеспечивает построение как комбинационных цепей, так и схем с

элементами памяти. Одна из макроячеек ЛБ показана на рис. 8.16. Из матрицы элементов

И в матрицу распределения термов МРТ поступает 5 основных термов (на рисунке слева).

МРТ дает возможность использовать эти термы для сборки по ИЛИ с последующей

подачей результата на элемент сложения по модулю 2 для образования комбинационной

функции, а также для управления триггером по входам сброса (CLR

n

), установки (PR

n

).

Терм t может быть использован для тактирования триггера или разрешения тактирования

в зависимости от программирования мультиплексора MUX2.

Триггер может тактироваться от глобального сигнала GCLK с минимальной задержкой

поступления сигнала синхронизации от общего входа микросхемы, что типично при

реализации синхронных автоматов. Тактирование от глобального сигнала может

сопровождаться индивидуальным управлением от сигнала разрешения тактирования ENA,

что характерно для построения апериодических автоматов, и, наконец, возможно

тактирование локальным сигналом от терма t, что соответствует асинхронным схемам.

417

Рис. 8.16. Схема макроячеек CPLD MAX 7000S

418

Имеются асинхронные сигналы установки и сброса PR

n

и CLR

n

, кроме того, сброс

возможен и от глобального сигнала GCLR при соответствующем программировании

мультиплексора MUX3.

Имеется возможность быстрой загрузки триггера от внешнего вывода по прямой цепи

(программируется мультиплексором MUX1). В другом состоянии MUX1 передает на вход

триггера значение функции, выработанное комбинационной частью макроячейки.

Мультиплексор MUX4 позволяет подавать на выход макроячейки (к БВВ) либо

непосредственно комбинационную функцию, либо хранящуюся в триггере (регистровый

выход).

Блок ввода/вывода (рис. 8.18) дает возможность гибкого управления разрешением

выходного буфера. ПМС формирует шесть глобальных сигналов разрешения выхода ОЕ.

Для некоторых представителей семейства МАХ 7000 имеется возможность

программирования выхода как выхода с открытым коллектором (ОК), кроме того, может

программироваться и скорость изменения выходных сигналов с целью, указанной ранее

(эта скорость связана с уровнем создаваемых помех).

Рис. 8.18. Схема блока ввода/вывода CPLD MAX 7000S

После семейства МАХ 7000, принадлежащего ко второму поколению CPLD, фирма Altera

выпустила семейство третьего поколения МАХ 9000. Между обоими семействами много

общего, но третьему поколению присущи и

420

новые свойства: интерфейс JTAG, программирование в системе ISP без применения

повышенных напряжений и др.

Развитие архитектур СБИС ПЛ идет по пути создания комбинированных структур,

сочетающих достоинства FPGA и CPLD. Так, например, фирма Altera выпустила

семейство FLEX 8000 (Flexible Logic Element MatriX) и позднее FLEX 10K с триггерной

памятью конфигурации.

Интерфейс JTAG и периферийное сканирование

Термином JTAG обозначают совокупность средств и операций, позволяющих проводить

тестирование БИС/СБИС без физического доступа к каждому ее выводу. Аббревиатура

JTAG возникла по наименованию разработчика - объединенной группы по тестам Joint

Test Action Group. Термином "периферийное сканирование" (ПС) или по-английски

Boundary Scan Testing (BST) называют тестирование по JTAG стандарту (IEEE Std 1149.1).

Такое тестирование возможно только для микросхем, внутри которых

439

имеется набор специальных элементов - ячеек периферийного сканирования (ячеек ПС), в

английской терминологии BSC (Boundary Scan Cells) и схем управления их работой.

Ячейки BSC размещены между каждым внешним выводом микросхемы и схемами

кристалла, образующими само проверяемое устройство. Все большее число современных

микросхем снабжается интерфейсом JTAG, т. е. возможностями периферийного

сканирования.

Основная концепция периферийного сканирования иллюстрируется рис. 8.24, a. Ячейки

сканирования BSC могут работать в разных режимах. В рабочем режиме они просто

пропускают сигналы через себя слева направо и не изменяют функционирования

устройства. При этом для выходов обычного логического типа нужна одна BSC, для

выходов с третьим состоянием - две (вторая для выработки сигнала управления буфером),

для двунаправленных выводов - три, что видно из рис. 8.24, а. Входные сигналы проходят

через ячейки BSC прямо к соответствующим точкам основных схем кристалла.

В режиме тестирования пропуск сигналов через ячейки прекращается, а сами они,

соединяясь последовательно, образуют сдвигающий регистр, обладающий также

некоторыми дополнительными функциями. В такой сдвигающий регистр со входа данных

тестирования может быть введен тестовый код для подачи на входные точки основной

схемы кристалла. Результат, который выработает основная схема, загружается в ячейки

BSC на ее выходах и затем выводится последовательно для сравнения с ожидаемым

правильным результатом вне устройства.

Периферийное сканирование позволяет проверять работу самих микросхем, монтажные

межсоединения микросхем между собой на печатной плате, считывать сигналы на

выводах микросхемы во время ее работы или управлять этими сигналами.

440

Рис. 8.24. Структура аппаратных средств интерфейса JTAG (а) и схема ячейки

периферийного сканирования (б)