Новиков А.А., Амелина М.А. Математическое моделирование в электронике. Курс лекций

Подождите немного. Документ загружается.

Проверка работы самих микросхем состоит в задании для них входного воздействия и

наблюдения за полученным результатом, проверка исправности монтажа микросхем на

плате осуществляется, например, при взаимодействии двух микросхем, имеющих JTAG

интерфейс. В этом случае тестирующая информация вводится в выходные ячейки одной

микросхемы, а затем

441

переписывается во входные ячейки другой. При исправности всех межсоединений

принятая информация идентична введенной.

С помощью расширения возможностей интерфейса JTAG можно производить также

реконфигурацию микросхем непосредственно в системе, без извлечения микросхем из

устройства.

СБИС программируемой логики типа "система на кристалле"

Уменьшение топологических норм проектирования и ряд технологических

усовершенствований довели уровень интеграции современных микросхем СБИС ПЛ до

величин в несколько миллионов эквивалентных вентилей, а быстродействие до тактовых

частот в 500...600 и более МГц. На таких кристаллах можно разместить целую систему

(процессорную часть, память, интерфейсные схемы и др.).

Определение СБИС как "система на кристалле" возникло вследствие двух факторов. Во-

первых, из-за высокого уровня интеграции, позволяющего разместить на кристалле схему

высокой сложности (систему). При этом разные по функционированию блоки

реализуются одними и теми же аппаратными средствами благодаря их

программируемости. Такие СБИС обозначаются в англоязычной литературе термином

generic. Во-вторых, из-за того, что СБИС приобретает специализированные области,

выделенные на кристалле для определенных функций - аппаратные ядра (Hardcores).

Системы разного назначения разделяются, тем не менее, на типовые части, что и ставит

вопрос о целесообразности введения в СБИС ПЛ наряду с программируемой логикой

специализированных областей с заранее определенными функциями.

Введение специализированных аппаратных ядер, имея ряд позитивных следствий, сужает

в то же время круг потребителей СБИС, поскольку в

425

сравнении с полностью программируемыми схемами (типа generic) уменьшается их

универсальность.

Реализация сложных функций специализированными аппаратными ядрами значительно

уменьшает площадь кристалла в сравнении с их реализациями на конфигурируемых

логических блоках. Для некоторых аппаратных ядер площадь снижается на порядок, для

других меньше. Например, умножитель 8×8, построенный по модифицированному

алгоритму Бута и реализованный методами заказного проектирования, разместился на

площади в 5 раз меньшей, чем такой же, реализованный на реконфигурируемых

логических блоках, обычных для взятой FPGA.

Таким образом, введение специализированных аппаратных ядер в FPGA и CPLD - процесс

противоречивый по результатам. Он сокращает площадь кристалла при реализации

сложных функций и ведет к достижению максимального быстродействия, но и таит в себе

нежелательные последствия для изготовителя СБИС, т. к. может ощутимо сузить рынок

их сбыта, а это ведет к росту цен и потере в какой-то мере конкурентоспособности

продукции.

Что же будет преобладать? Здесь ключевой вопрос - какие именно специализированные

аппаратные ядра будут выбраны для реализации.

Самый очевидный выбор - блоки ОЗУ. Эти блоки в той или иной мере нужны почти для

всех систем, причем некоторые из них требуют очень больших объемов памяти.

Выяснились уже и условия эффективного использования ядер памяти - не слишком

крупные блоки, возможность изменять организацию памяти, возможность иметь

асинхронный и синхронный режимы работы, организовывать буферы FIFO и

двухпортовую память. Многие FPGA уже давно основываются на SRAM-ячейках (обычно

на каждый конфигурируемый ЛБ тратится 16...32 бит ОЗУ), и эти ячейки могут быть

применены не только для конфигурирования ЛБ, но и организуются в простые ОЗУ,

которые могут далее объединяться в более емкие регистровые файлы. Однако такой

вариант не дает максимального быстродействия и существенно снижает количество

доступной пользователю логики кристалла, т. к. каждые 16...32 бита памяти "выводят из

строя" целый ЛБ, т. е. по эквивалентной сложности 10...20 логических вентилей.

В среднем блок ОЗУ с заказным проектированием емкостью 256...512 бит может быть

реализован на площади в приблизительно 1/10 от той, которая затрачивается на подобный

блок, составленный из распределенных на кристалле ячеек памяти конфигурации.

Времена доступа также уменьшаются в 1,5...4 раза.

Области ОЗУ- первые и, безусловно, главные специализированные аппаратные ядра.

Других не так уж много. Это умножители, используемые в некоторых СБИС ПЛ, а также

схемы интерфейса JTAG. Ядра интерфейса JTAG успешно внедрились во многие СБИС

ПЛ, поскольку они выполняют важные функции, нужные очень многим, занимают очень

небольшую площадь на кристалле и позволяют достичь высокого быстродействия.

426

Самыми сложными из практически известных ядер являются контроллеры шины PCI,

также необходимые в очень многих приложениях и требующие максимального

быстродействия.

Средства описания проекта

Применение САПР требует эффективных, наглядных, управляемых и контролируемых

средств описания проекта. Описать проектируемое устройство можно разными

способами, причем обычно применяют способ, пригодный для описания проекта в целом.

Методы описания, применимые исключительно для отдельных фрагментов устройства,

относятся к числу редких.

В настоящее время к наиболее распространенным универсальным способам описания,

применимым для любого уровня иерархии проекта, относят графический и текстовый.

Реже используются непосредственная разводка схем FPGA в редакторе топологии,

описания в виде требуемых временных диаграмм и др. Каждый из способов описания

проекта имеет свои достоинства и недостатки. Сходство способа описания и внутренней

организации и поведения разрабатываемого устройства существенно сокращает время

создания проекта, упрощает его тестирование и, как правило, оказывается наиболее

наглядным и понятным.

Графическое представление проекта создается в базисе допустимых для выбранной САПР

библиотечных элементов, например, в базисе элементов стандартной серии ТТЛ(Ш).

Главное достоинство графического способа - его традиционность и наглядность,

связанные с привычностью разработчиков к восприятию изображений схем. Конечно, это

преимущество проявляется только при правильном иерархическом и структурном

разбиении проекта.

Современные языки описания аппаратуры (HDL, Hardware Description Languages)

допускают описание проектируемого устройства, как с точки зрения его поведения, так и с

точки зрения его структуры. Эти возможности делают все более распространенным

представление проекта в форме текстового описания алгоритмов функционирования его

фрагментов в сочетании с текстовым же описанием межблочных соединений для сложных

проектов. Достоинства текстового способа описания проекта заключаются в его

компактности и относительной простоте автоматизации любых преобразований, включая

начальную генерацию описания проекта. Очень важна возможность использования

стандартных универсальных языков типа HDL, обеспечивающая простоту переноса

проекта с одной аппаратной платформы на другую и переход от одной САПР к другой.

В отличие от текстовых, графические способы представления проекта обычно узко

специализированы и требуют особых средств для переноса информации о проекте в

другую среду, для чего могут быть применены специальные универсальные языки

передачи информации о проекте (типа языка EDIF, Electronic Design Interchange Format).

Языковое описание аппаратуры получает все большее распространение. Текстовые

описания имеют две основные разновидности - языки низкого уровня (аналоги языков

программирования типа ассемблера) и высокого уровня.

459

459 :: Содержание

460 :: Содержание

Языки низкого уровня

Языки низкого уровня ближе к аппаратным средствам, вследствие чего представляют для

компиляторов потенциальные возможности создания проектов с более выигрышными

параметрами. Платой за это является обычно жесткая ориентация на определенную

аппаратуру и производящую ее фирму. Примерами таких языков могут служить язык

AHDL (Altera HDL) и ABEL (фирмы Xilinx). С помощью языков низкого уровня легче

создавать проекты с наилучшими временными параметрами, т. к. в проектах будут учтены

специфические особенности архитектуры той или иной CPLD или FPGA.

460

460 :: Содержание

460 :: Содержание

Языки высокого уровня

Языки высокого уровня менее связаны с аппаратными платформами и поэтому более

универсальны. Среди них наиболее распространены языки VHDL и Verilog. Эти языки,

как и другие алгоритмические языки высокого уровня, в принципе позволяют описать

любой алгоритм в последовательной форме, т. е. через последовательность операторов

присвоения и принятия решений. Основное их отличие в способности отражать также и

параллельно исполняемые в аппаратуре действия, представляемые отдельными

параллельно выполняемыми процессами с общим инициализирующим воздействием.

СИСТЕМА ПРОЕКТИРОВАНИЯ MAX PLUS

Название системы MAX+PLUS II является аббревиатурой от Multiple Array MatriX Programmable

Logic User System (Пользовательская система программирования логики упорядоченных структур).

Система MAX+PLUS II разработана фирмой Altera и обеспечивает многоплатформенную архитектурно

независимую среду создания дизайна, легко приспосабливаемую для конкретных требований

пользователя. Система MAX+PLUS II имеет средства удобного ввода дизайна, быстрого прогона и

непосредственного программирования устройств.

Система MAX+PLUS II предлагает полный спектр возможностей логического дизайна: разнообразные

средства описания проекта для создания проектов с иерархической структурой, мощный логический

синтез, компиляцию с заданными временными параметрами, разделение на части, функциональное и

временное тестирование (симуляцию), тестирование нескольких связанных устройств, анализ

временных параметров системы, автоматическую локализацию ошибок, а также программирование и

верификацию устройств. В системе MAX+PLUS II можно как читать, так и записывать файлы на языке

AHDL и файлы трассировки в формате EDIF, файлы на языках описания аппаратуры Verilog HDL и

VHDL а также схемные файлы OrCAD. Кроме того, система MAX+PLUS II читает файлов трассировки,

созданных с помощью ПО Xilinx, и записывает файлы задержек в формате SDF для удобства

взаимодействия с пакетами, работающими с другими промышленными стандартами.

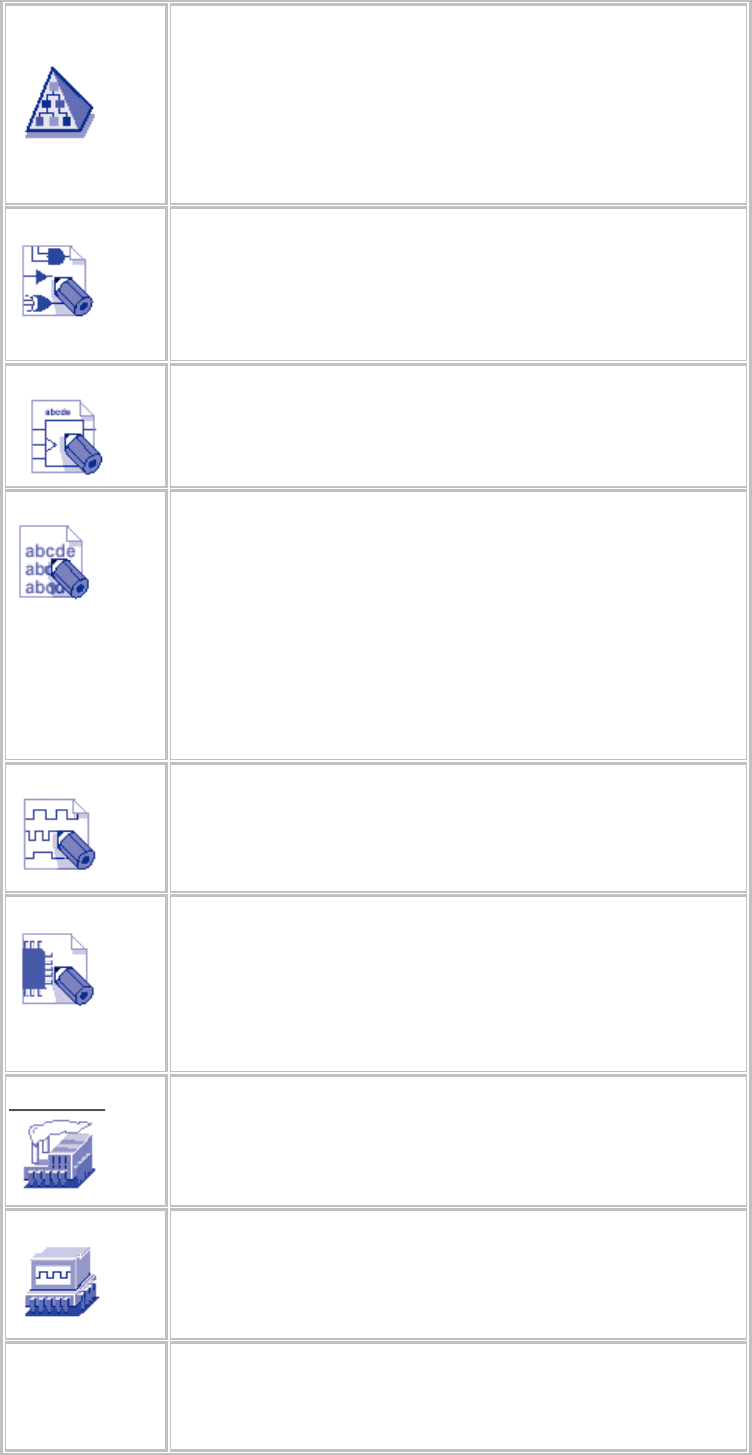

В полную систему MAX+PLUS II входят 11 полностью внедренных в систему приложений (рис. 2.2).

(Логический дизайн (design), включая все поддизайны (subdesign), называется в системе MAX+PLUS II

проектом (project))

Рис. 2.2. Приложения в системе MAX+PLUS II

I. Для ввода описания проекта (Design Entry) возможно описание проекта в виде файла на языке

описания аппаратуры, созданного либо во внешнем редакторе, либо в текстовом редакторе MAX+PLUS II

(Text Editor), в виде схемы электрической принципиальной с помощью графического редактора Graphic

Editor, в виде временной диаграммы, созданной в сигнальном редакторе Waveform Editor. Для удобства

работы со сложными иерархическими проектами каждому поддизайну может быть сопоставлен символ,

редактирование которого производится с помощью графического редактора Symbol Editor. Размещение

узлов по ЛБ и выводам ПЛИС выполняют с помощью поуровневого планировщика Floorplan Editor.

II. Компиляция проекта, включая извличение списка соединений (Netlist Extractor), построение базы

данных проекта (Data Base Builder), логический синтез (logic synthesis), извлечение временных,

функциональных параметров проекта (SNF Extractor), разбиение на части (Partioner), трассировка (Fitter) и

формирование файла программирования или загрузки (Assembler) выполняются с помощью компилятора

системы (Compiler)

Наиболее важные этапы компиляции:

Модуль логического синтезатора (Logic Synthesizer) применяет ряд алгоритмов, которые уменьшают

использование ресурсов и убирают дублированную логику, обеспечивая тем самым максимально

эффективное использование структуры логического элемента для архитектуры целевого семейства

устройств.

Если проект не помещается при монтаже в одно устройство, модуль Partitioner (разделитель)

разделяет базу данных, обновленную логическим синтезатором, на несколько ПЛИС одного и того же

семейства, стараясь при этом разделить проект на минимально возможное число устройств. Разбиение

проекта происходит по границам логических элементов, а число выводов, используемое для сообщения

между устройствами, минимизируется.

Используя базу данных, обновленную модулем разбиения, модуль трассировки (Fitter) приводит в

соответствие требования проекта с известными ресурсами одного или нескольких устройств. Он

назначает каждой логической функции расположение реализующего ее логического элемента и

выбирает соответствующие пути взаимных соединений и назначения выводов.

Functional SNF Extractor (экстрактор для функционального тестирования)создает файл для

функционального тестирования (.snf). Этот функциональный файл SNF не содержит информации о

временных параметрах.

Timing SNF Extractor (экстрактор для тестирования временных параметров) создает (если

компиляция проекта прошла без ошибок) файл для тестирования временных параметров (.snf), который

содержит данные о временных параметрах проекта. Этот файл используется для тестирования и анализа

временных параметров.

Assembler (модуль ассемблера)

Модуль ассемблера преобразует назначения логических элементов, выводов и устройства, сделанные

модулем трассировки Fitter, в программный образ для устройства (устройств) в виде одного или

нескольких двоичных объектных файлов, содержащие информацию для программатора, которые

обрабатываются программатором системы MAX PLUS II и программирующей аппаратурой фирмы

Altera (или другим программатором).

III. Верификация проекта (Project verification) выполняется с помощью симулятора (simulator),

результаты работы которого удобно просмотреть в сигнальном редакторе Waveform Editor, в нем же

создаются тестовые воздействия.

В САПР МАХ + PLUS II предусмотрено автоматическое вычисление трех основных

классов временных параметров (модуль Timing Analyzer):

минимальных и максимальных задержек между источниками (входными

сигналами) и приемниками (выходными сигналами), информация о которых

выдается в виде матрицы задержек;

максимально возможной производительности устройства (пропускной

способности) в виде максимальной частоты тактирования элементов памяти,

используемых в проекте;

времен предустановки и выдержки сигналов, гарантирующих надежную работу

схем при фиксации сигналов в синхронных элементах памяти.

IV. Программирование ПЛИС. Непосредственно программирование или загрузка конфигурации

устройств с использованием соответствующего аппаратного обеспечения выполняется с

использованием модуля программатора (Programmer).

В табл. 2.3 приведены пиктограммы и описание приложений.

Таблица 2.3

Приложения системы MAX+PLUS II

Приложение Выполняемая функция

Hierarchy

Display

Обзор иерархии – отображает текущую иерархическую

структуру файлов в виде дерева с ветвями, представляющими

собой поддизайны. Можно визуально определить, является ли

файл проекта схемным, текстовым или сигнальным; какие файлы

открыты в данный момент; какие вспомогательные файлы в

проекте доступны пользователю для редактирования. Можно

также непосредственно открыть или закрыть один или несколько

файлов дерева и ввести назначения ресурсов для них

Graphic Editor Графический редактор – позволяет разрабатывать схемный

логический дизайн в формате реального отображения на экране

WYSIWYG. Применяя разработанные фирмой Altera примитивы,

мегафункции и макрофункции в качестве основных блоков

разработки, пользователь может также использовать собственные

символы

Symbol Editor Символьный редактор – позволяет редактировать

существующие символы и создавать новые

Text Editor Текстовый редактор – позволяет создавать и редактировать

текстовые файлы проекта, написанные на языках описания

аппаратуры AHDL, VHDL и Verilog HDL. Кроме того, в этом

редакторе можно создавать, просматривать и редактировать

другие файлы формата ASCII, используемые другими

приложениями MAX+PLUS II. Можно создавать файлы на языках

HDL и в других текстовых редакторах, однако данный текстовый

редактор системы MAX+PLUS II дает преимущества в виде

контекстной справки, выделения цветом синтаксических

конструкций и готовых шаблонов языков AHDL, VHDL и Verilog

HDL

Waveform Editor Сигнальный редактор – выполняет двойную функцию:

инструмент для разработки дизайна и инструмент для ввода

тестовых сигналов и наблюдения результатов тестирования

Floorplan Editor Поуровневый планировщик – позволяет графическими

средствами делать назначения выводам устройства и ресурсов

логических элементов и блоков. Можно редактировать

расположение выводов на чертеже корпуса устройства и

назначать сигналы отдельным логическим элементам на более

подробной схеме логической структуры (LAB view). Можно

также просматривать результаты последней компиляции

Compiler Компилятор – обрабатывает логические проекты, разработанные

для семейств устройств Altera Classic. MAX 5000, MAX 7000,

MAX 9000, FLEX 6000, FLEX 8000 и FLEX 10K. Большинство

заданий выполняется автоматически. Однако пользователь может

управлять процессом компиляции полнеостью или частично

Simulator Симулятор – позволяет тестировать логические операции и

внутреннюю синхронизацию проектируемой логической схемы.

Возможны три режима тестирования: функциональное,

временное и тестирование нескольких соединенных между собой

устройств

Timing Analyzer Анализатор временных параметров – анализирует работу

проектируемой логической цепи после того, как она была

синтезирована и оптимизирована компилятором, позволяет

оценить задержки, возникающие в схеме.

Programmer Программатор – позволяет программировать, конфигурировать,

проводить верификацию и испытывать устройства фирмы Altera

Message

Processor

Генератор сообщений – выдает на экран сообщения об ошибках,

предупреждающие и информационные сообщения о состоянии

проекта пользователя и позволяет пользователю автоматически

найти источник сообщения в исходном или вспомогательном

файле (файлах) и в поуровневом плане назначений