Кубанский Государственный Технологический Университет. Факультет

КТАС. 4 курс. Специальность 230101 (Вычислительные машины,

комплексы, системы и сети)

Теоретические вопросы:

Понятие операционной системы и операционной среды.

Классификация системного программного обеспечения.

Понятие вычислительного процесса и ресурса. Основные виды ресурсов.

Диаграмма состояний процесса. Процессы и потоки.

Понятие прерывания. Виды прерываний. Схемы обработки прерываний.

Особенности 32-х разрядных процессоров Intel. Основные группы регистров.

Реальный и защищенный режимы 32-х разрядных процессоров Intel.

Адресация в защищенном режиме 32-х разрядных процессорах Intel.

Структура дескриптора сегмента и типы сегментов памяти в защищенном режиме 32-х разрядных процессоров Intel. Селекторы.

Глобальная и локальные дескрипторные таблицы 32-х разрядных процессоров Intel. Структура дескриптора сегмента памяти и селектора дескриптора.

Сегментный способ адресации в защищенном режиме 32-х разрядных процессоров Intel.

Страничный способ адресации в защищенном режиме 32-х разрядных процессоров Intel.

Режим виртуальной машины (V86) для исполнения программ реального режима. Прерывания и исключения в режиме V

86. Монитор виртуальной машины.

Защита адресного пространства задач. Локальное и глобальное адресное пространство.

Уровни привилегий и кольца защиты 32-х разрядных процессоров Intel.

Защита задач по уровням привилегий. Правила защиты при обращении к сегментам в 32-х разрядных процессорах Intel.

Защита задач по уровням привилегий. Правила защиты при передаче управления в 32-х разрядных процессорах Intel.

Системные дескрипторы и шлюзы 32-х разрядных процессоров Intel.

Многозадачность 32-х разрядных процессоров Intel. Сегмент состояния задачи (TSS) и его дескриптор. Регистр задачи (TR).

Многозадачность 32-х разрядных процессоров Intel. Команды переключения задач и вложенные задачи. Роль флага NT при переключении задач.

Механизм шлюзов для организации переключения задач. Структура и виды шлюзов.

Обработка аппаратных прерываний и исключений в защищенном режиме 32-х разрядных процессоров Intel. Структура и виды шлюзов.

Обработка прерываний и исключений в контексте текущей задачи.

Обработка прерываний и исключений с переключением на новую задачу.

Дескрипторная таблица прерываний (IDT). Шлюз прерываний и шлюз ловушки.

Контроллер прерываний IBM PC совместимых компьютеров. Структура контроллера. Каскадирование контроллеров прерываний.

Планирование и диспетчеризация процессов и задач. Стратегии планирования. Качество и гарантии обслуживания.

Планирование и диспетчеризация процессов и задач. Дисциплины диспетчеризации.

Планирование и диспетчеризация процессов и задач. Вытесняющая и не вытесняющая многозадачность. Диспетчеризация с использованием динамических приоритетов.

Виртуальное адресное пространство и способы распределения памяти. Непрерывные способы распределения памяти.

Виртуальное адресное пространство и способы распределения памяти. Разрывные способы распределения памяти. Страничное распределение памяти.

Виртуальное адресное пространство и способы распределения памяти. Разрывные способы распределения памяти. Сегментное распределение памяти.

Виртуальное адресное пространство и способы распределения памяти. Разрывные способы распределения памяти. Сегментно-страничное распределение памяти. Практические задания:

Привести пример фрагмента кода на языке ассемблера, переводящий микропроцессор в защищенный режим. Считать, что дескрипторная таблица GDT уже подготовлена и все поля дескрипторов заполнены.

Привести пример фрагмента кода на языке ассемблера, переводящий микропроцессор обратно в реальный режим. При возврате восстановить работу системы прерываний реального режима (настроить регистр IDTR).

Привести пример фрагмента кода на языке ассемблера, включающий механизм страничного преобразования адреса и заполняющий соответствующие таблицы преобразования.

Привести пример фрагмента кода на языке ассемблера, перепрограммирующий ведущий контроллер прерывания на новый базовый вектор 20h. Считать, что в системе имеются два контроллера прерывания и что ведомый контроллер подключен ко второй линии IRQ ведущего.

Привести пример фрагмента кода на языке ассемблера, перепрограммирующий ведомый контроллер прерывания на новый базовый вектор 28h. Считать, что ведомый контроллер подключен ко второй линии IRQ ведущего.

Привести пример фрагмента кода на языке ассемблера, маскирующий прерывания с номерами IRQ 1, 3, 5, 7, 11 и затем восстанавливающий исходную маску для обоих контроллеров прерываний.

Привести пример кода на языке ассемблера, маскирующий прерывания с номерами IRQ 1, 8, 10, 12, 14, и затем восстанавливающий исходную маску для обоих контроллеров прерываний.

Привести пример фрагмента кода на языке ассемблера, позволяющий производить обработку прерываний и исключений в защищенном режиме, а также содержимое IDT. Считать, что обработка ведется общими для группы обработчиками. Ведущий контроллер настроен на векторы прерываний от 20h до 27h, а ведомый от 28h до 2Fh.

Привести пример фрагмента кода на языке ассемблера, позволяющий организовать переключение задач в защищенном режиме, а также заполняющий минимальный набор полей сегмента состояния задачи TSS, необходимых для переключения на новую задачу.

Привести пример фрагмента кода на языке ассемблера, работающий с сегментами на различных уровнях привилегий, а также представить содержимое глобальной дескрипторной таблицы, созданной при этом.

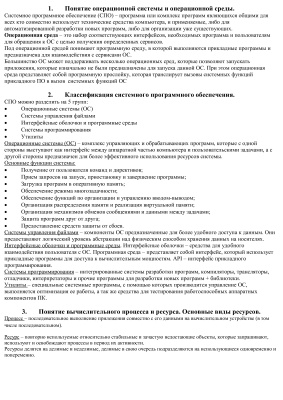

Понятие операционной системы и операционной среды.

Классификация системного программного обеспечения.

Понятие вычислительного процесса и ресурса. Основные виды ресурсов.

Диаграмма состояний процесса. Процессы и потоки.

Понятие прерывания. Виды прерываний. Схемы обработки прерываний.

Особенности 32-х разрядных процессоров Intel. Основные группы регистров.

Реальный и защищенный режимы 32-х разрядных процессоров Intel.

Адресация в защищенном режиме 32-х разрядных процессорах Intel.

Структура дескриптора сегмента и типы сегментов памяти в защищенном режиме 32-х разрядных процессоров Intel. Селекторы.

Глобальная и локальные дескрипторные таблицы 32-х разрядных процессоров Intel. Структура дескриптора сегмента памяти и селектора дескриптора.

Сегментный способ адресации в защищенном режиме 32-х разрядных процессоров Intel.

Страничный способ адресации в защищенном режиме 32-х разрядных процессоров Intel.

Режим виртуальной машины (V86) для исполнения программ реального режима. Прерывания и исключения в режиме V

86. Монитор виртуальной машины.

Защита адресного пространства задач. Локальное и глобальное адресное пространство.

Уровни привилегий и кольца защиты 32-х разрядных процессоров Intel.

Защита задач по уровням привилегий. Правила защиты при обращении к сегментам в 32-х разрядных процессорах Intel.

Защита задач по уровням привилегий. Правила защиты при передаче управления в 32-х разрядных процессорах Intel.

Системные дескрипторы и шлюзы 32-х разрядных процессоров Intel.

Многозадачность 32-х разрядных процессоров Intel. Сегмент состояния задачи (TSS) и его дескриптор. Регистр задачи (TR).

Многозадачность 32-х разрядных процессоров Intel. Команды переключения задач и вложенные задачи. Роль флага NT при переключении задач.

Механизм шлюзов для организации переключения задач. Структура и виды шлюзов.

Обработка аппаратных прерываний и исключений в защищенном режиме 32-х разрядных процессоров Intel. Структура и виды шлюзов.

Обработка прерываний и исключений в контексте текущей задачи.

Обработка прерываний и исключений с переключением на новую задачу.

Дескрипторная таблица прерываний (IDT). Шлюз прерываний и шлюз ловушки.

Контроллер прерываний IBM PC совместимых компьютеров. Структура контроллера. Каскадирование контроллеров прерываний.

Планирование и диспетчеризация процессов и задач. Стратегии планирования. Качество и гарантии обслуживания.

Планирование и диспетчеризация процессов и задач. Дисциплины диспетчеризации.

Планирование и диспетчеризация процессов и задач. Вытесняющая и не вытесняющая многозадачность. Диспетчеризация с использованием динамических приоритетов.

Виртуальное адресное пространство и способы распределения памяти. Непрерывные способы распределения памяти.

Виртуальное адресное пространство и способы распределения памяти. Разрывные способы распределения памяти. Страничное распределение памяти.

Виртуальное адресное пространство и способы распределения памяти. Разрывные способы распределения памяти. Сегментное распределение памяти.

Виртуальное адресное пространство и способы распределения памяти. Разрывные способы распределения памяти. Сегментно-страничное распределение памяти. Практические задания:

Привести пример фрагмента кода на языке ассемблера, переводящий микропроцессор в защищенный режим. Считать, что дескрипторная таблица GDT уже подготовлена и все поля дескрипторов заполнены.

Привести пример фрагмента кода на языке ассемблера, переводящий микропроцессор обратно в реальный режим. При возврате восстановить работу системы прерываний реального режима (настроить регистр IDTR).

Привести пример фрагмента кода на языке ассемблера, включающий механизм страничного преобразования адреса и заполняющий соответствующие таблицы преобразования.

Привести пример фрагмента кода на языке ассемблера, перепрограммирующий ведущий контроллер прерывания на новый базовый вектор 20h. Считать, что в системе имеются два контроллера прерывания и что ведомый контроллер подключен ко второй линии IRQ ведущего.

Привести пример фрагмента кода на языке ассемблера, перепрограммирующий ведомый контроллер прерывания на новый базовый вектор 28h. Считать, что ведомый контроллер подключен ко второй линии IRQ ведущего.

Привести пример фрагмента кода на языке ассемблера, маскирующий прерывания с номерами IRQ 1, 3, 5, 7, 11 и затем восстанавливающий исходную маску для обоих контроллеров прерываний.

Привести пример кода на языке ассемблера, маскирующий прерывания с номерами IRQ 1, 8, 10, 12, 14, и затем восстанавливающий исходную маску для обоих контроллеров прерываний.

Привести пример фрагмента кода на языке ассемблера, позволяющий производить обработку прерываний и исключений в защищенном режиме, а также содержимое IDT. Считать, что обработка ведется общими для группы обработчиками. Ведущий контроллер настроен на векторы прерываний от 20h до 27h, а ведомый от 28h до 2Fh.

Привести пример фрагмента кода на языке ассемблера, позволяющий организовать переключение задач в защищенном режиме, а также заполняющий минимальный набор полей сегмента состояния задачи TSS, необходимых для переключения на новую задачу.

Привести пример фрагмента кода на языке ассемблера, работающий с сегментами на различных уровнях привилегий, а также представить содержимое глобальной дескрипторной таблицы, созданной при этом.