Базарова И.А. Организация ЭВМ и систем

Подождите немного. Документ загружается.

71

2. Сравнение - используется для сравнения элементов данных по

величине или на равенство.

3. Преобразование форматов.

4. Логические операции («и», «и-не», «или», «исключающее или»)

5. Операции сдвига

6. Пересылка данных между регистрами MMX

7. Очистка регистров MMX

Для расширения возможностей технологии MMX компания AMD

ввела технологию 3DNow! Эта технология позволяет оперировать с но-

вым типом данных – упакованные числа в

формате с плавающей точкой.

Достоинство: 3DNow! даёт заметный результата при работе с гра-

фикой и при этом сохраняется программная совместимость с предыду-

щими моделями процессоров и ОС.

Типы данных 32-х разрядных процессоров

1. Бит

2. Битовое поле (до 32 разрядов)

3. Битовая строка (до 4 Гб)

4. Байт

5. Числа без знак (8/16/32/64)

6. Числа со

знаком (8/16/32/64)

7. Числа в формате с плавающей точкой

8. Двоично-десятичные

9. Строки байт, слов, двойных слов

10. Указатели (селекторы, смещение)

Система команд

Система команд 32-х разрядных процессоров является расшире-

нием системы команд 16 разрядных процессоров. Расширения касаются

увеличения разрядности адресов, операндов, боле гибкой системы ад-

ресации и новые типы данных.

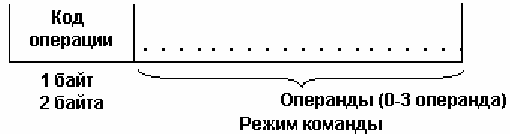

Команда

состоит из двух полей: одно поле отводится под код опе-

рации, оставшееся поле отводится под операнды.

72

Рис. 35. Структура команды.

Операнды могут извлекаться из регистра процессора, из памяти и

ли находиться непосредственно в самой инструкции. Перед любой инст-

рукцией может использоваться префикс. Они используются для работы

со строковыми операциями, для изменения разрядности слова адреса,

префикс захвата локальной шины.

Основные группы инструкций:

1. Инструкции пересылки данных. Позволяют

передавать константы,

переменные между регистрами, памятью и портами ввода/вывода.

2. Инструкции двоичной арифметики. Выполняют все действия над

двоичными числами.

3. Инструкции десятичной арифметики. Является дополнением ко

второй группе.

4. Инструкции логических операций. Выполняют функции булевой

алгебры-логики над байтами, словами, двойными словами.

5. Сдвиги и вращения (циклические сдвиги). Выполняются над реги-

страми

или операндом в памяти.

6. Инструкции обработки бит и байт.

7. Инструкции передачи управления – это инструкции условных и

безусловных переходов, вызовов процедур и прерываний.

Безусловный переход бывает внутрисегментным или межсегментным.

Внутрисегментный делится на:

a) Короткий переход от –128

÷

127 байт по убыванию

b) Ближний переход (любые расстояния внутри сегмента)

8. Команды по управлению со строковыми операциями.

9. Операции с флагами. Позволяют менять значение отдельных

флагов, сохранять эти значения в стеке и восстанавливать.

10. Инструкции загрузки указателей. Позволяют загружать дальние

указатели из памяти в РОН и соответствующий сегментный ре-

гистр.

11. Инструкции MMX.

12.

Инструкции математического сопроцессора.

73

13. Системные инструкции. К ним относятся инструкции управления

защитой – загрузка и сохранение регистров дескрипторов и реги-

стров задач, проверка привилегий, обмен с управляющими, отла-

дочными и модельно специфическими регистрами, инструкции по

управлению кэшированием, инструкции захвата шины и остановка

процессора.

§4.6. Защищенный режим

Защищенный режим (PVAM – Protected Virtual Address Mode) явля-

ется основным режимом работы 32-х

разрядных процессоров. Он пред-

назначен для обеспечения независимого выполнения нескольких задач,

что подразумевает защиту ресурсов одной задачи от воздействия дру-

гой. Главным защищаемым ресурсом является память, а также совмест-

но используемая аппаратура, обращение к которой происходит через

операции ввода/вывода и прерывания. Большинство функций защиты

процессор реализует на программном уровне, а

часть функций – на ап-

паратном.

Характеристики защищенного режима

1. Защита памяти основана на сегментации.

Максимальный размер сегмента – 4 Гб. В защищенном режиме

сегменты распределяются ОС. Прикладная программа может использо-

вать только разрешенные для нее сегменты памяти, выбирая их с по-

мощью селекторов из дескрипторных таблиц.

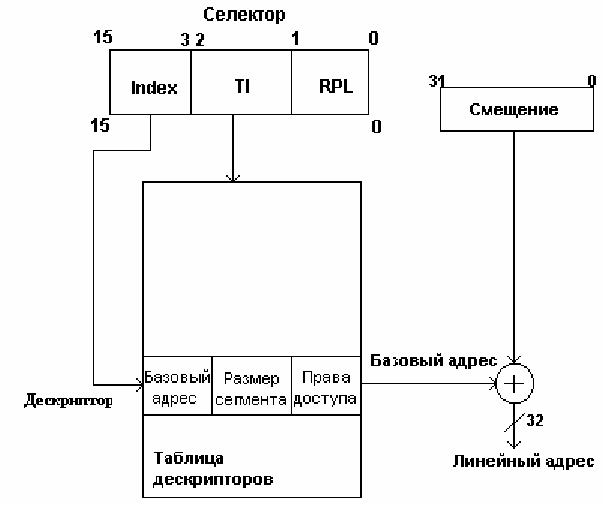

Процессор может обращаться только к

тем сегментам памяти, для

которых имеются дескрипторы в таблицах. Механизм сегментации фор-

мирует линейный адрес по следующей схеме:

74

Рис. 36. Вычисление линейного адреса в защищённом режиме.

Селектор – это логическое имя модулей кодов или данных.

Поле TI принимает значение либо «0», либо «1».

Если TI = 0 GDT (выбирается глобальная таблица дескрипторов)

Если TI = 1 LDT (выбирается локальная таблица дескрипторов)

2. Защита памяти с помощью сегментации не позволяет:

Использовать сегменты не по назначению

Нарушать права доступа

Адресоваться

к элементам выходящим за лимит сегмента

Изменять содержимое таблицы дескрипторов, не имея достаточ-

ных привилегий.

3. Защищенный режим предоставляет средства переключения за-

дач. Состояние каждой задачи сохраняется в сегменте состоя-

ния задачи. При переключении задач, состояние текущей зада-

чи автоматически сохраняется в ее TSS (сегмент состояния за-

дачи).

4. Четырехуровневая иерархическая система

привилегий.

Предназначена для управления использованием

привилегированных инструкций и доступа к дескрипторам.

Передача управления между задачами контролируется

вентилями (шлюзы), проверяющими правила использования

уровня привилегий. Уровни привилегий:

PL0 - самый приоритетный уровень привилегий, относится к ядру ОС.

75

PL1 – отводится под системные сервисы

PL2 – относится к расширениям ОС

PL3 – приложения

Уровни привилегий также относятся к дескрипторам, селекторам,

задачам, а также инструкции ввода/вывода. Нарушение защиты вызыва-

ет исключения.

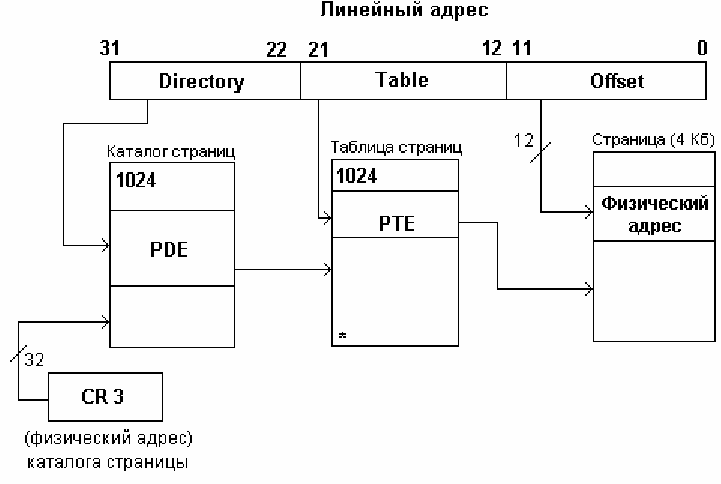

5. Страничное управление памятью является средством органи-

зации виртуальной памяти с подкачкой страниц по запросу.

Сегментация организует программы и данные в модули опре

-

делённого размера, а страничная организация оперирует с па-

мятью как с набором страниц одинакового размера. В момент

обращения страница может присутствовать в физической опе-

ративной памяти или быть выгруженной на внешнюю память.

При обращении к выгруженной странице процессор вырабаты-

вает исключение – отказ страницы. При этом программный об-

работчик исключений получает

необходимую информацию для

свопинга.

В оперативной памяти в каждый момент времени следует хранить

только небольшие области сегментов, необходимые активным задачам.

Эту возможность обеспечивает страничное управление памятью.

Базовый механизм страничного управления использует двухуров-

невую табличную трансляцию линейного адреса в физический.

Рис. 37. Базовый механизм страничной переадресации.

76

Механизм защиты страниц использует два уровня привилегий:

1 уровень – пользователь

2 уровень – супервизор

Пользователю соответствует уровень привилегий 3. Супервизору – 0, 1, 2.

Для того, чтобы работать со страницей увеличенного размера ис-

пользуется режим PSE (Page Size Extension). При таком режиме выпа-

дает Table и таблица страниц.

Кроме этих режимов страничной переадресации возможна переад-

ресация в режимах для страниц 4 Кб и

2 Мб (размер страниц всегда

одинаковый).

6. Виртуализация прерываний. В многозадачной системе с разде-

ляемыми устройствами внешние прерывания изначально обра-

батываются ОС, которая определяет, к какой задаче относится

каждое конкретное прерывание. Задача, которая должна обра-

батывать аппаратные прерывания может получать их как в ре-

альном виде, так и в виртуальном. Если приложению

передают-

ся реальные прерывания, то использование виртуальной памя-

ти с подкачкой страниц станет занимать слишком много време-

ни, что является критичным для обработчиков прерываний.

Чтобы избежать подкачки страниц по аппаратным прерывани-

ям, обработчики прерываний должны располагаться в ядре ОС,

постоянно присутствующем в памяти.

Если задача находится в непрерывном состоянии, то

ОС может

сообщить о прерывании только после перехода в прерываемое состоя-

ние. Такие прерывания называются виртуальными.

7. В защищенном режиме возможно использовать режим вирту-

ального 8086 процессора.

Глава 5. Архитектура памяти

§ 5.1. Принципы кэширования

Основная память компьютеров реализуется на относительно мед-

ленной динамической памяти (DRAM), обращение к ней приводит к про-

стою процессора — появляются такты ожидания (wait states). Статиче-

ская память (SRAM), построенная, как и процессор, на триггерных ячей-

ках, по своей природе способна догнать современные процессоры по

быстродействию и сделать ненужными такты ожидания (или хотя бы со-

77

кратить их количество). Разумным компромиссом для построения эко-

номичных и производительных систем явился иерархический способ ор-

ганизации оперативной памяти. Идея заключается в сочетании основной

памяти большого объема на DRAM с относительно небольшой кэш-па-

мятью на быстродействующих микросхемах SRAM.

В переводе слово кэш (cache) означает «тайный склад», «тайник»

(«заначка»). Тайна этого склада заключается

в его «прозрачности» —

для программы он не представляет собой дополнительной адресуемой

области памяти. Кэш является дополнительным быстродействующим

хранилищем копий блоков информации из основной памяти, вероят-

ность обращения к которым в ближайшее время велика. Кэш не может

хранить копию всей основной памяти, поскольку его объем во много раз

меньше основной памяти. Он

хранит лишь ограниченное количество

блоков данных и каталог (cache directory) — список их текущего соответ-

ствия областям основной памяти. Кроме того, кэшироваться может не

вся память, доступная процессору.

При каждом обращении к памяти контроллер кэш-памяти по ката-

логу проверяет, есть ли действительная копия затребованных данных в

кэше. Если она там есть, то

это случай кэш-попадания (cache hit), и дан-

ные берутся из кэш-памяти. Если действительной копии там нет, это

случай кэш-промаха (cache miss), и данные берутся из основной памяти.

В соответствии с алгоритмом кэширования блок данных, считанный из

основной памяти, при определенных условиях заместит один из блоков

кэша. От интеллектуальности алгоритма замещения зависит процент

попаданий и, следовательно, эффективность кэширования. Поиск блока

в списке должен производиться достаточно быстро, чтобы «задум-

чивостью» в принятии решения не свести на нет выигрыш от примене-

ния быстродействующей памяти. Обращение к основной памяти может

начинаться одновременно с поиском в каталоге, а в случае попадания —

прерываться (архитектура Look aside). Это экономит время, но

лишние

обращения к основной памяти ведут к увеличению энергопотребления.

Другой вариант: обращение к внешней памяти начинается только после

фиксации промаха (архитектура Look Through), при этом теряется по

крайней мере один такт процессора, зато экономится энергия.

В современных компьютерах кэш обычно строится по двухуровне-

вой схеме. Первичный кэш (LI Cache) встроен во все процессоры класса

486

и старше; это внутренний кэш. Объем этого кэша невелик (8-32

78

Кбайт). Для повышения производительности для данных и команд часто

используется раздельный кэш (так называемая Гарвардская архитекту-

ра — противоположность Принстонской, использующей общую память

для команд и данных). Вторичный кэш (L2 Cache) для процессоров 486 и

Pentium является внешним (устанавливается на системной плате), а у

Р6 располагается в одной упаковке с ядром и подключается к специаль-

ной внутренней шине процессора.

Кэш-контроллер должен обеспечивать когерентность (coherency) —

согласованность данных кэш-памяти обоих уровней с данными в основ-

ной памяти, при том условии, что обращение к этим данным может про-

изводиться не только процессором, но и другими активными (busmaster)

адаптерами, подключенными к шинам (PCI, VLB, ISA и т. д.). Следует

также учесть, что процессоров

может быть несколько, и у каждого может

быть свой внутренний кэш.

Контроллер кэша оперирует строками (cache line) фиксированной

длины. Строка может хранить копию блока основной памяти, размер ко-

торого, естественно, совпадает с длиной строки. С каждой строкой кэша

связана информация об адресе скопированного в нее блока основной

памяти и об ее состоянии.

Строка может быть действительной (valid) —

это означает, что в текущий момент времени она достоверно отражает

соответствующий блок основной памяти, или недействительной. Ин-

формация о том, какой именно блок занимает данную строку (то есть

старшая часть адреса или номер страницы), и о ее состоянии называет-

ся тегом (tag) и хранится в связанной с данной

строкой ячейке специ-

альной памяти тегов (tag RAM). В операциях обмена с основной памя-

тью обычно строка участвует целиком (несекторированный кэш), для

процессоров 486 и старше длина строки совпадает с объемом данных,

передаваемых за один пакетный цикл (для 486 это 4х4=16 байт, для

Pentium 4х8=32 байт). Возможен и вариант секторированного (sectored)

кэша, при котором одна строка

содержит несколько смежных ячеек —

секторов, размер которых соответствует минимальной порции обмена

данных кэша с основной памятью. При этом в записи каталога, соответ-

ствующей каждой строке, должны храниться биты действительности для

каждого сектора данной строки. Секторирование позволяет экономить

память, необходимую для хранения каталога при увеличении объема

кэша, поскольку большее количество бит

каталога отводится под тег и

выгоднее использовать дополнительные биты действительности, чем

увеличивать глубину индекса (количество элементов) каталога.

79

Строки кэша под отображение блока памяти выделяются при про-

махах операций чтения, в Р6 строки заполняются и при записи. Запись

блока, не имеющего копии в кэше, производится в основную память (для

повышения быстродействия запись может производиться через буфер

отложенной записи). Поведение кэш-контроллера при операции записи

в память, когда копия затребованной

области находится в некоторой

строке кэша, определяется его алгоритмом, или политикой записи (Write

Policy). Существуют две основные политики записи данных из кэша в

основную память: сквозная запись WT (Write Through) и обратная запись

WB (Write Back).

Политика WT предусматривает выполнение каждой операции за-

писи (даже однобайтной), попадающей в кэшированный блок, одновре-

менно и в строку кэша, и в

основную память. При этом процессору при

каждой операции записи придется выполнять относительно длительную

запись в основную память. Алгоритм достаточно прост в реализации и

легко обеспечивает целостность данных за счет постоянного совпаде-

ния копий данных в кэше и основной памяти. Для него не нужно хранить

признаки присутствия и модифицированности — вполне достаточно

только

информации тега (при этом считается, что любая строка всегда

отражает какой-либо блок, а какой именно — указывает тег). Но эта

простота оборачивается низкой эффективностью записи. Существуют

варианты этого алгоритма с применением отложенной буферированной

записи, при которой данные в основную память переписываются через

FIFO-буфер во время свободных тактов шины.

Политика WB позволяет

уменьшить количество операций записи

на шине основной памяти. Если блок памяти, в который должна произ-

водиться запись, отображен в кэше, то физическая запись сначала бу-

дет произведена в эту действительную строку кэша, и она будет отме-

чена как грязная (dirty), или модифицированная, то есть требующая вы-

грузки в основную память. Только

после этой выгрузки (записи в основ-

ную память) строка станет чистой (clean), и ее можно будет использо-

вать для кэширования других блоков без потери целостности данных. В

основную память данные переписываются только целой строкой. Эта

выгрузка контроллером может откладываться до наступления крайней

необходимости (обращение к кэшированной памяти другим абонентом,

замещение в кэше

новыми данными) или выполняться в свободное

время после модификации всей строки. Данный алгоритм сложнее в

80

реализации, но существенно эффективнее, чем WT. Поддержка систем-

ной платой кэширования с обратной записью требует обработки допол-

нительных интерфейсных сигналов для выгрузки модифицированных

строк в основную память, если к этой области производится обращение

со стороны таких контроллеров шины, как другие процессоры, графиче-

ские адаптеры, контроллеры дисков, сетевые адаптеры и т. п.

Работу

внутренней кэш-памяти характеризуют следующие процес-

сы: обслуживание запросов процессора на обращение к памяти, выде-

ление и замещение строк для кэширования областей физической памя-

ти, обеспечение согласованности данных внутреннего кэша и оператив-

ной памяти, управление кэшированием.

Внутренний запрос процессора на обращение к памяти направля-

ется во внутренний кэш. В случае

попадания (Cache Hit), запрос на чте-

ние обслуживается только кэш-памятью, не выходя на внешнюю шину.

Запрос на запись модифицирует данную строку и в зависимости от

поли-

тики записи на внешнюю шину выходит либо сразу (при сквозной записи),

либо несколько позже при использовании алгоритма обратной записи.

В случае промаха (Cache Miss) запрос на запись направляется

только на внешнюю шину, при запросе на чтение, если этот запрос отно-

сится к кэшируемой области памяти, выполняется цикл заполнения це-

лой строки кэша

– все 16 байт (32 — для Pentium) читаются из опера-

тивной памяти и помещаются в одну из строк набора кэша, обслужи-

вающего данный адрес. Если затребованные данные не укладываются в

одной строке, заполняется и соседняя. Заполнение строки процессор

старается выполнить самым быстрым способом — пакетным циклом с

32-битными передачами (64-битными для Pentium и старше).

Внутренний запрос

процессора на данные удовлетворяется сразу,

как только затребованные данные считываются из ОЗУ. Если в наборе

имеется свободная строка, заполнена будет именно она и для нее ус-

тановится бит достоверности. Если свободных строк в наборе нет, будет

замещена строка, к которой дольше всех не было обращений.

Таким образом, выделение и замещение

строк выполняется только для

КЭШ-промахов чтения, при промахах записи заполнение строк не произ-

водится. Кроме того, существует возможность аннулирования строк –

объявления недостоверными и очистки всей кэш-памяти.

Очистка внутренней кэш-памяти при сквозной записи осуществля-

ется внешним сигналом FLUSH# за один такт системной шины (по сиг-