Хмелевский И.В., Битюцкий В.П. Организация ЭВМ и систем. Однопроцессорные ЭВМ. Часть 4

Подождите немного. Документ загружается.

40

====================================================================

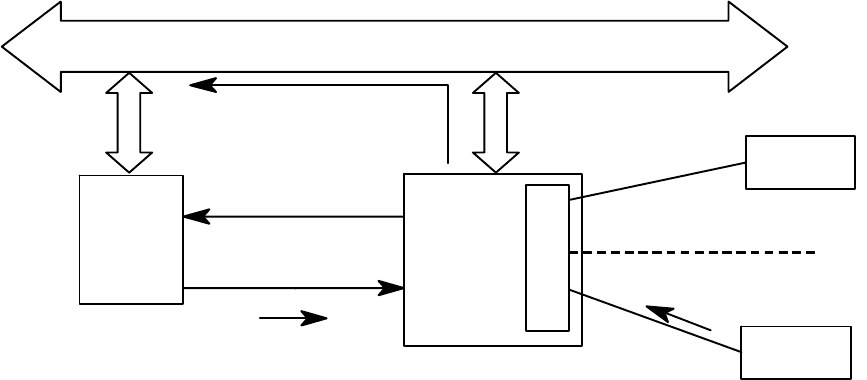

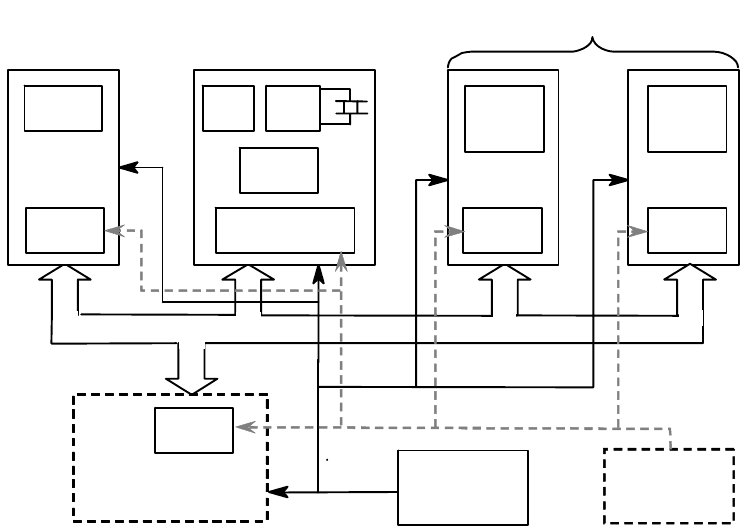

ИЗП – источник запросов прерывания;

ЗП – сигнал запроса прерывания;

ПП – сигнал подтверждения прерывания;

ОСП – общий сигнал прерывания;

ЛЗП – линия запросов прерывания;

ЛПП – линия подтверждения прерывания;

РгЗП – регистр запросов прерывания

Рис. 6.5. Радиальная структура системы прерывания

ЗП

k

А

дрес вектора

прерывания

Шина данных (ШД)

Процес-

сор

Контрол-

лер пре-

рываний

ИЗП

1

ОСП

ЛПП

ПП

ИЗП

k

ЛЗП

i

ЛЗП

1

ЛЗП

k

РгЗП

====================================================================

41

====================================================================

2

Адрес вектора

прерывания

ЛПП

k

ЛПП

ПП

Шина данных (ШД)

Процес-

сор

ОСП

ИЗП

j

ИЗП

1

ИЗП

m

ЛЗП

1

ЛЗП

i

ЗП

j

ЛЗП

k

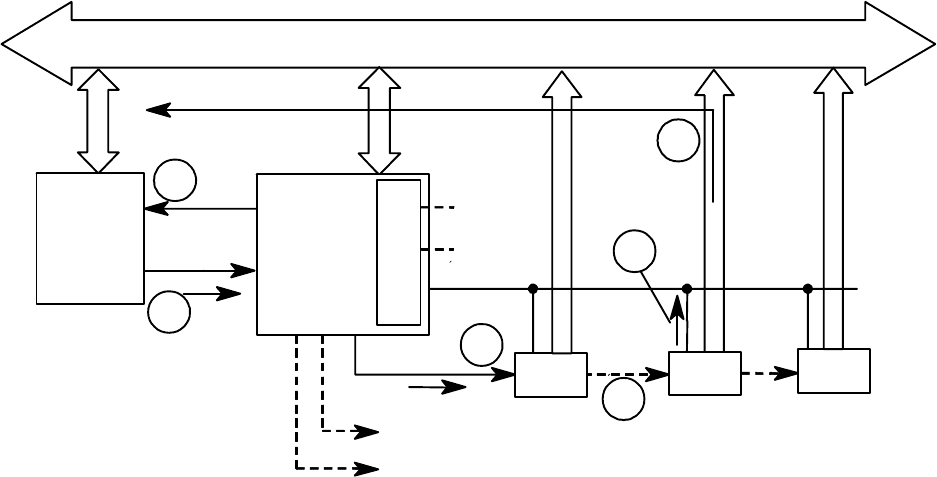

ИЗП – источник запросов прерывания;

ЗП – сигнал запроса прерывания;

ПП – сигнал подтверждения прерывания;

ОСП – общий сигнал прерывания;

ЛЗП – линия запросов прерывания;

ЛПП – линия подтверждения прерывания

Рис. 6.6. Цепочечная структура системы прерывания

(цифрами обозначена последовательность прохождения сигналов)

ПП

k

ЛПП

i

ЛПП

1

Контрол-

лер пре-

рываний

РгЗП

3

4

5

6

1

====================================================================

42

====================================================================

ОСП

Сброс

1

n

2

1

&

R

S

T

Код номера

запроса

Счетчик

ГТИ

k=2

n

2 1

Дешифратор

ЗП

1

ЗП

2

ЗП

k

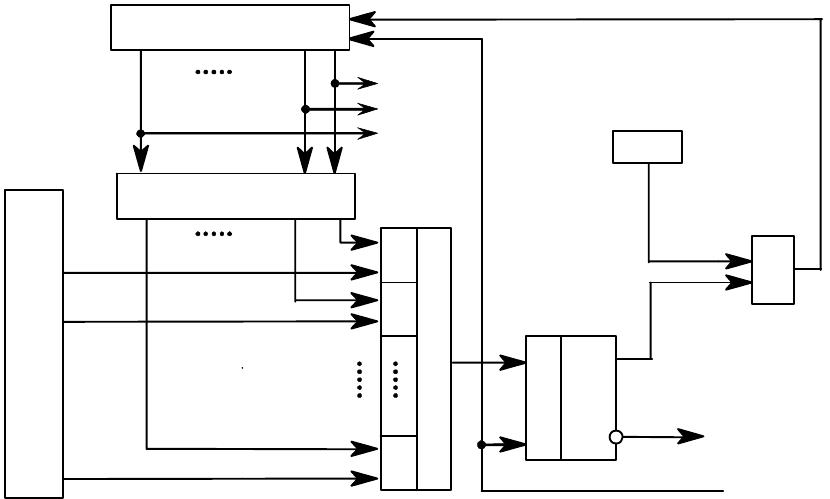

РгЗП – регистр запросов прерываний;

ЗП – запрос на прерывание;

ОСП – общий сигнал запроса на прерывание;

ГТИ – генератор тактовых импульсов

Рис. 6.7. Схема устройства циклического опроса РгЗП

&

&

&

РгЗП

====================================================================

43

====================================================================

Сигнал ПП

y

3

&

1

1

&

1'

&

2

&

2'

&

3

&

3'

Шифратор номера максимального приоритета

ОСП

y

1

y

2

ЗП

1

ЗП

2

ЗП

3

Сигнал

"Приоритет"

Порог прерывания

ОСП

Код адреса

вектора прерывания

РгЗП

Компаратор

&

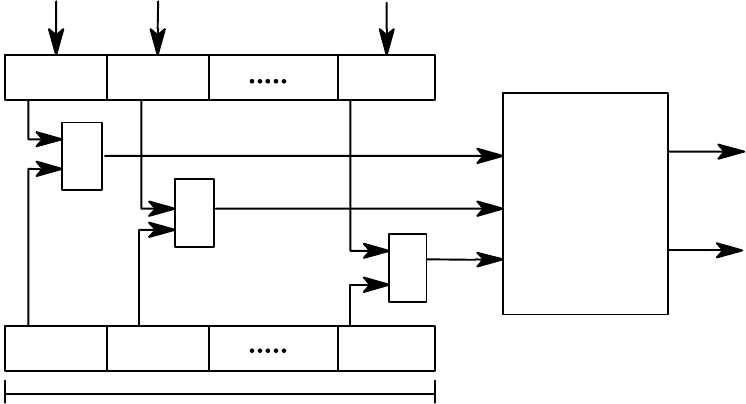

ПП – подтверждение прерывания;

ОСП – общий сигнал прерывания;

ЗП – запрос прерывания;

РгЗП – регистр запросов прерываний

Рис. 6.8. Схема устройства однотактного опроса РгЗП

====================================================================

44

====================================================================

Код приоритетного

запроса

Код маски

&

1 2 k

1 2 k

Схема

выделения

незамаски-

рованных

запросов

макс. при-

оритета

&

&

РгМ

РгЗП

ОСП

ЗП

1

ЗП

2

ЗП

k

ЗП – запрос на прерывание;

РгЗП – регистр запросов прерываний;

РгМ – регистр маски;

ОСП – общий сигнал прерывания

Рис. 6.9. Схема реализации управления приоритетами

с помощью маски прерывания

====================================================================

45

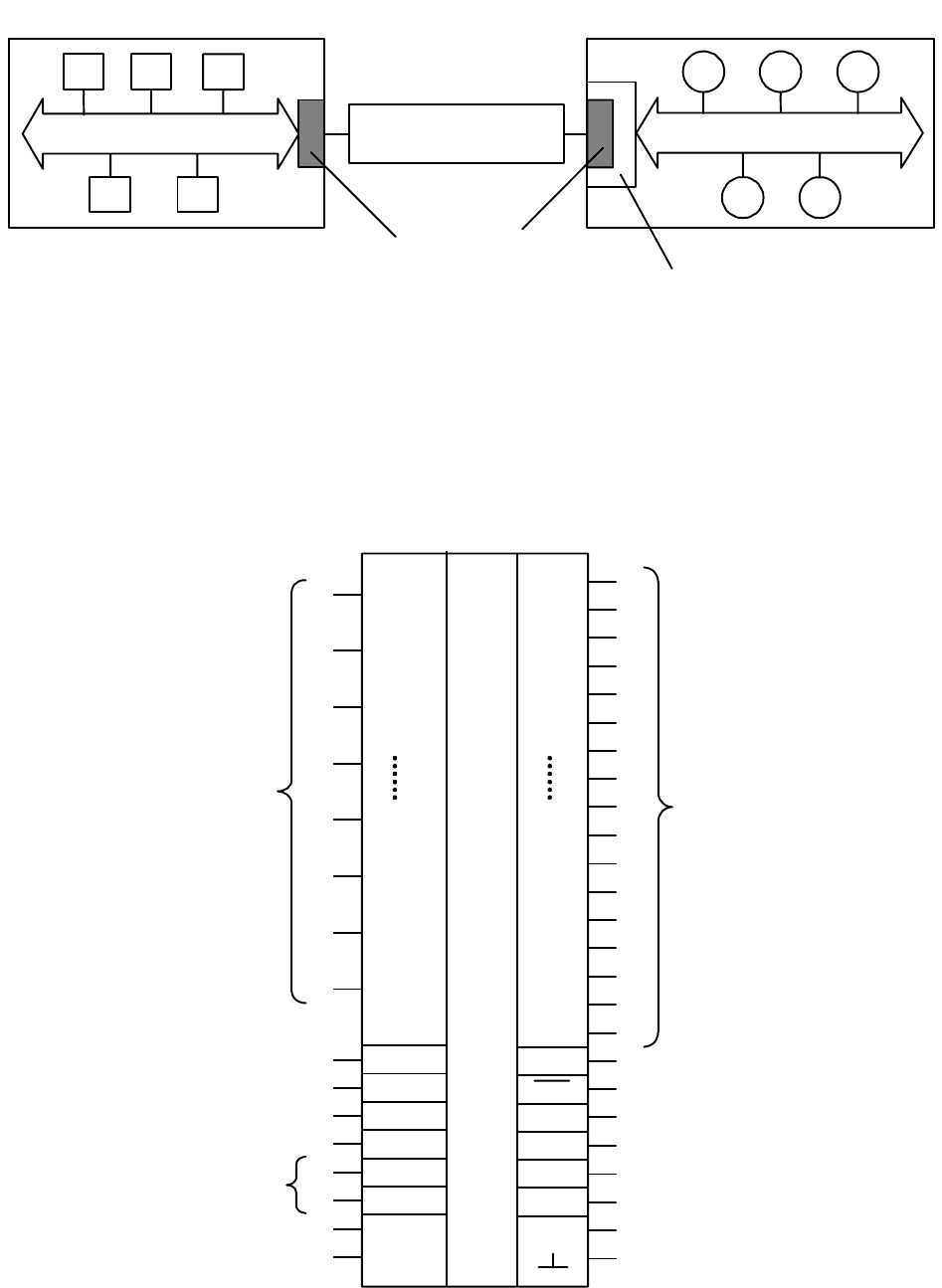

7. Простейшая микроЭВМ

====================================================================

ППУ

УСОМ

Модуль В/В

МП

ВСУУ

УСОМ УСОМ УСОМ

ОЗУ

(RAM)

ПЗУ

(ROM)

Модуль процессора

Сл

у

ж.

индикатор

и клавиат

у

ра

УСОМ

Модуль памяти

БП

Общая магистраль

ППУ – приёмопередающее устройство;

УСОМ – устройство сопряжения с общей магистралью

МП – микропроцессор;

ГТИ – генератор тактовых импульсов;

ВСУУ – вспомогательные устройства управления;

ПЗУ – постоянное запоминающее устройство;

ОЗУ – оперативно запоминающее устройство;

БП – блок питания;

ГТИом – генератор тактовых импульсов общей магистрали

Рис. 7.1. Обобщенная структура простейшей микроЭВМ

ГТИом

ГТИ

====================================================================

46

ПРОЦЕС

СОР

Шина адреса

Шина данных

Шина упр-я

Шина данных ввода/вывода

Шина управления ввода/вывода

К ППУ

а

б

Шина данных

Шина управления

К памяти

К ППУ

в

Шина адреса/данных

Шина адреса ввода/вывода

К

п

а

м

я

т

и

К памяти

К ППУ

ПРОЦЕС

СОР

ПРОЦЕС

СОР

Шина адреса

I/O R/W

Шина управления I/O R/W

г

ПРОЦЕС

СОР

Шина данных

Шина управления

К памяти

К ППУ

д

Шина адреса/данных

Шина управления

К памяти

К ППУ

Рис. 7.2. Структуры микро-ЭВМ:

а – с раздельными шинами; б – с изолированными шинами;

в – с изолированными шинами и мультиплексированием шин,

адресов и данных; г – с общими шинами; д – с общими шинами

и мультиплексированием шин адресов и данных

Шина адреса

ПРОЦЕС

СОР

====================================================================

47

====================================================================

Системный интерфейс

Промежуточный

интерфейс

Внутренний интерфейс

Адаптеры

промежуточного

интерфейса

(или ППУ)

Контроллер ПУ

МикроЭВМ Периферийное устройство

ППУ – приемопередающее устройство;

ПУ – переферийное устройство

Рис. 7.3. Включение промежуточного стандартного интерфейса

====================================================================

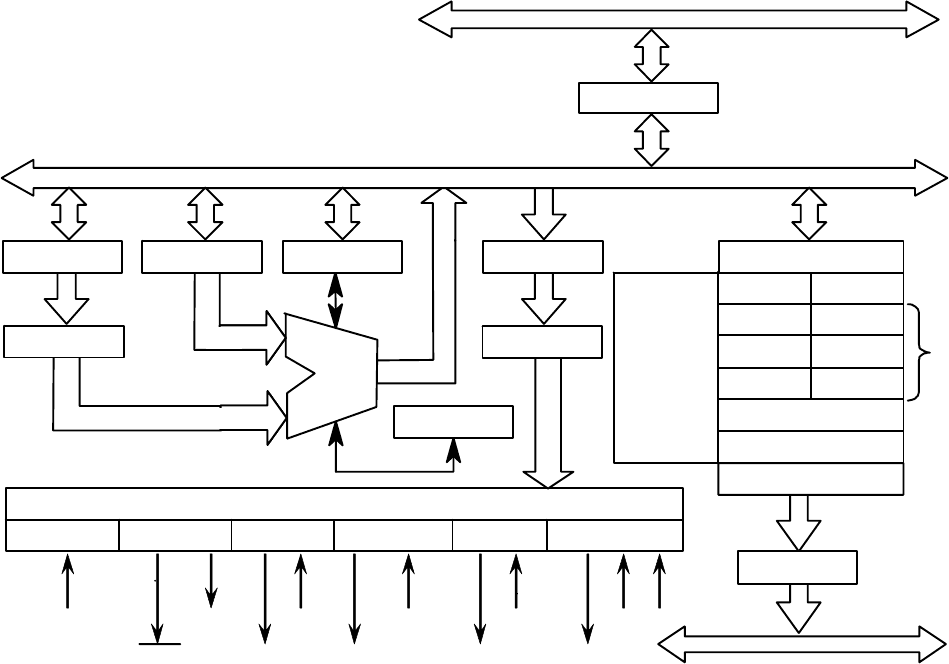

Рис. 7.4. Условное обозначение МП КР580ВМ80

Шина ад

р

еса

25

26

27

28

29

30

31

32

33

34

35

1

40

38

39

37

36

17

18

16

19

24

28

21

2

DBIN

W

R

INTE

SYNC

HLDA

WAIT

+12В

А

0

А

15

CPU

10

9

8

7

3

4

5

6

13

12

23

14

15

20

22

11

HOLD

RESET

READY

INT

F

1

F

2

+5В

D

0

D

7

-5В

Шина данных

Сигналы

синхронизации

====================================================================

48

====================================================================

БД

Внешняя ШД

(ШД системного интерфейса)

РгА (8)

БР2

(

8

)

БР1

(

8

)

РгП

(

5

)

Мультиплексор

БА

РгК (8)

Д

шК

(

8

)

СДК

А

ЛУ

(

8

)

Устройство

у

правления и синхронизация

Упр. сч. к. Чтен./зап.Прерыв. Ожидание Обмен Синхрониз.

W

(

8

)

Z

(

8

)

B (8)

C (8)

D

(

8

)

E

(

8

)

H (8)

L

(

8

)

SP (16)

PC (16)

PA (16)

Схема

выбора

регист-

ров

Внешняя ША

(ША системного интерфейса)

РОН

RESET

W

R

DBIN

INTE

INT

WAIT

READY

HLDA

HLD

SYNC

F

1

F

2

Внутренняя ШД МП

РгА – аккумулятор; БД – буфер данных;

РгП – регистр признаков; БА – буфер адреса;

БР1, БР2 – буферные регистры; SP – указатель стека;

РгК – регистр команд; PC – счетчик адреса команд;

ДшК – дешифратор команд; PA – регистр адреса;

СДК – схема десятичной коррекции; РОН – регистр общего назначения;

ША – шина адреса; АЛУ – арифметико-логическое устройство

Рис. 7.5. Функциональная схема МП

====================================================================

49

====================================================================

Вход. лог.

элемент

Выход. лог.

элемент

Внешняя ШД

Внутренняя ШД МП

Буфер ШД

Управляющие

сигналы

Рис. 7.6. Функциональная схема буфера ШД МП

====================================================================

B C

7 0 7 0

000

010

100

001

011

101

111

D E

H L

A

PC

SP

F

15

0

7

0

РгП

1

– триггер разрешения прерывания

Рис. 7.7. МП с точки зрения программиста

====================================================================

S Z 0 V 0 P 1 C

7 6 543 2 1 0

Номер разряда

s – знаковый (0 – положительный результат, 1 – отрицательный результат);

z – нулевой результат (1 – результат равен нулю, 0 – результат не равен нулю);

v – дополнительный перенос из 3-го в 4-й разряд (1 – есть перенос, 0 – нет переноса);

p – четность числа единиц в результате; (1 – четное число, 0 – нечетное число);

c – перенос из 7-го разряда (1 – есть перенос, 0 – нет переноса)

Рис. 7.8. Регистр признаков

====================================================================