Сушкин И.Н. Вычислительная техника и информационные технологии

Подождите немного. Документ загружается.

20

прерывания используются различные регистры процессора (счетчик команд,

регистр состояния и т. д.), то информацию, содержащуюся в них в момент

прерывания, необходимо сохранить для последующего возврата в прерван-

ную программу. Обычно задача сохранения содержимого счетчика команд и

регистра состояния процессора возлагается на аппаратные средства обработ-

ки прерывания. Сохранение содержимого других регистров процессора, ис-

пользуемых в подпрограмме обработки прерывания, производится непосред-

ственно в подпрограмме. Отсюда следует достаточно очевидный факт: чем

больший объем информации о прерванной программе сохраняется про-

граммным путем, тем больше время реакции МПС на сигнал прерывания, и

наоборот. Предпочтительными с точки зрения повышения производительно-

сти МПС (сокращения времени выполнения подпрограмм обработки, а, сле-

довательно, и основной программы) являются уменьшение числа команд,

обеспечивающих сохранение информации о прерванной программе, и реали-

зация этих функций аппаратными средствами.

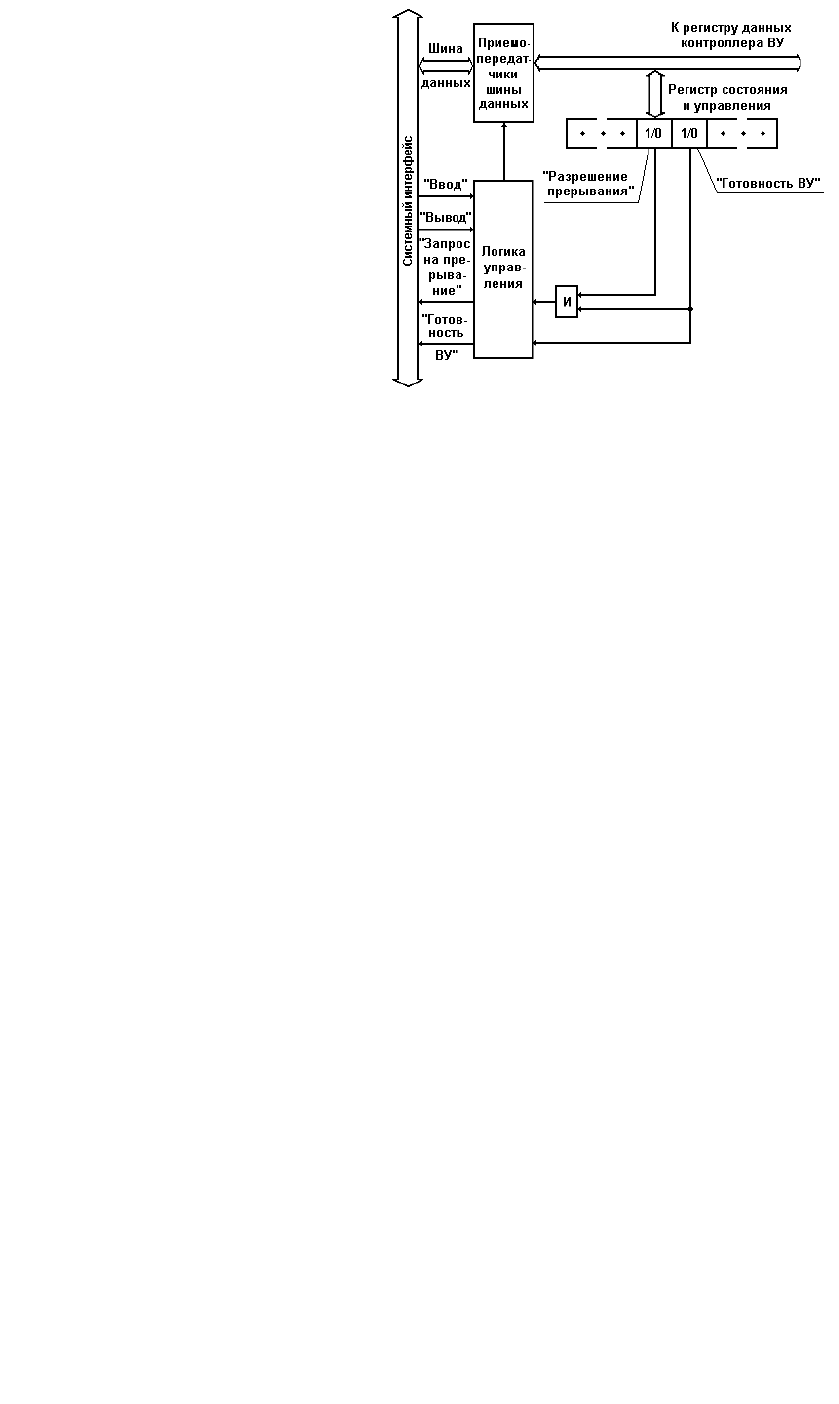

Формирование сигналов прерываний – запросов ВУ на обслуживание

происходит в контроллерах соответствующих ВУ. В простейших случаях в

качестве сигнала прерывания может использоваться сигнал «Готовность

ВУ», поступающий в системный интерфейс МПС (например, из АЦП). Одна-

ко такое простое решение обладает существенным недостатком: процессор

не имеет возможности управлять прерываниями, т. е. разрешать или запре-

щать их для отдельных ВУ. В результате организация обмена данными в ре-

жиме прерывания с несколькими ВУ существенно усложняется. Для решения

этой проблемы регистр состояния и управления контроллера ВУ (рис. 12) до-

полняют еще одним разрядом – «Разрешение прерывания». Запись 1 или 0 в

разряд «Разрешение прерывания» производится программным путем по од-

ной из линий шины данных системного интерфейса.

Управляющий сигнал системного интерфейса «Запрос на прерывание»

формируется с помощью схемы совпадения только при наличии единиц в

разрядах «Готовность ВУ» и «Разрешение прерывания» регистра состояния и

управления контроллера. Аналогичным путем решается проблемам управле-

ния прерываниями в МПС в целом. Для этого в регистре состояния процес-

сора выделяется разряд, содержимое которого определяет, разрешены или

запрещены прерывания от внешних устройств. Значение этого разряда может

устанавливаться программным путем.

21

Рис. 12. Фрагмент блок-схемы контроллера ВУ с разрядом «Разреше-

ние прерывания» в регистре состояния и управления

В МПС обычно используется одноуровневая система прерываний, т. е.

сигналы «Запрос на прерывание» от всех ВУ поступают на один вход про-

цессора. Поэтому возникает проблема идентификации ВУ, запросившего об-

служивание, и реализации заданной очередности (приоритета) обслуживания

ВУ при одновременном поступлении нескольких сигналов прерывания. Су-

ществуют два основных способа идентификации ВУ, запросивших обслужи-

вания:

- программный опрос регистров состояния (разряд «Готовность ВУ»)

контроллеров всех ВУ (работа по опросу);

- использование векторов прерывания (работа по запросу).

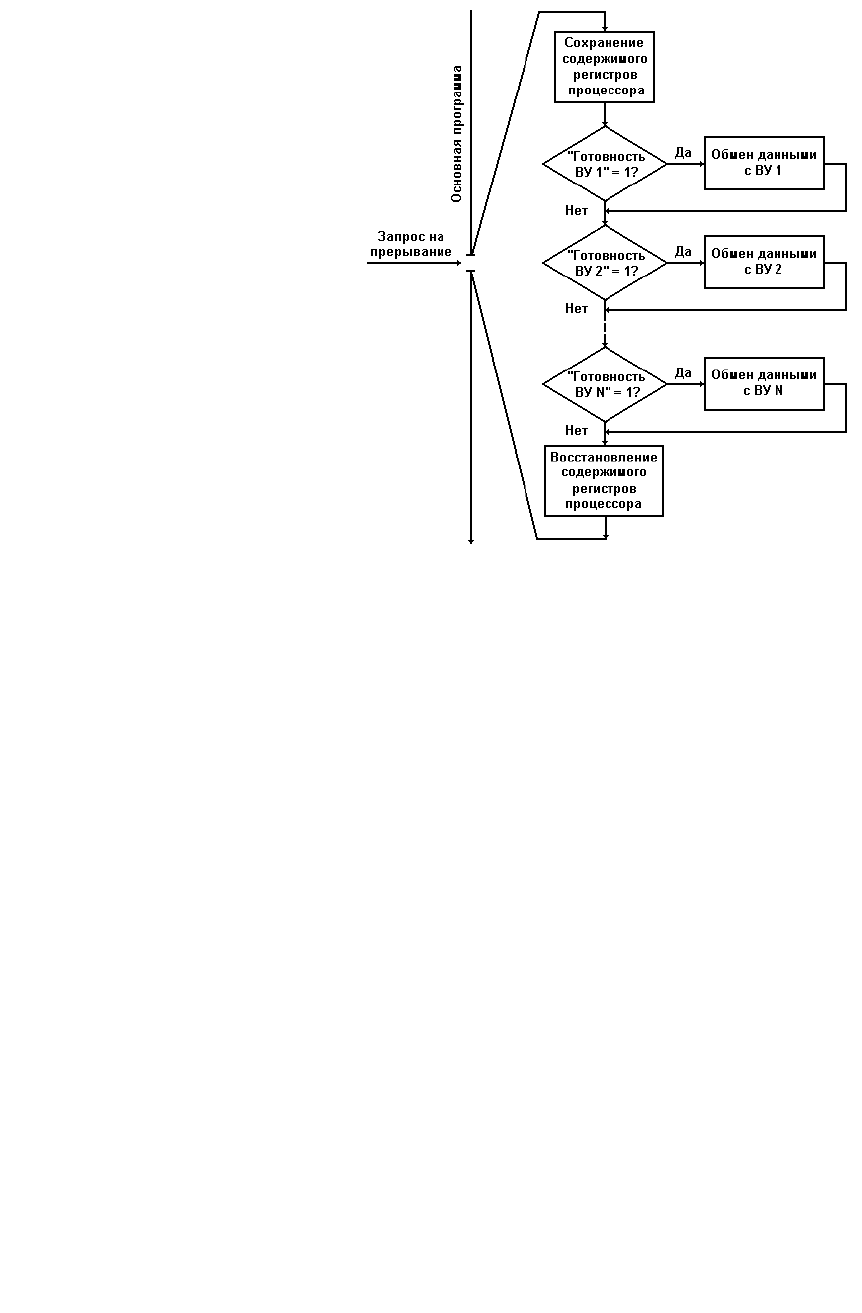

Организация прерываний с программным опросом готовности предпо-

лагает наличие в памяти МПС единой подпрограммы обслуживания преры-

ваний от всех внешних устройств. Структура такой подпрограммы приведена

на рис. 13.

Обслуживание ВУ с помощью единой подпрограммы обработки пре-

рываний производится следующим образом. В конце последнего машинного

цикла выполнения очередной команды основной программы процессор про-

веряет наличие требования прерывания от ВУ. Если сигнал прерывания есть

и в процессоре прерывание разрешено, то процессор переключается на вы-

полнение подпрограммы обработки прерываний. После сохранения содер-

жимого регистров процессора, используемых в подпрограмме, начинается

последовательный опрос регистров состояния контроллеров всех ВУ, рабо-

тающих в режиме прерывания. Как только подпрограмма обнаружит готовое

к обмену ВУ, сразу выполняются действия по его обслуживанию. Завершает-

22

ся подпрограмма обработки прерывания после опроса готовности всех ВУ и

восстановления содержимого регистров процессора.

Рис. 13. Структура единой программы обработки прерываний

и её связь с основной программой

Приоритет ВУ в микроЭВМ с программным опросом готовности

внешнего устройства однозначно определяется порядком их опроса в под-

программе обработки прерываний. Чем раньше в подпрограмме опрашивает-

ся готовность ВУ, тем меньше время реакции на его запрос и выше приори-

тет. Необходимость проверки готовности всех внешних устройств сущест-

венно увеличивает время обслуживания тех ВУ, которые опрашиваются по-

следними. Это является основным недостатком рассматриваемого способа

организации прерываний. Поэтому обслуживание прерываний с опросом го-

товности ВУ используется только в тех случаях, когда отсутствуют жесткие

требования на время обработки сигналов прерывания внешних устройств.

Организация системы прерываний в микроЭВМ с использованием век-

торов прерываний позволяет устранить указанный недостаток. При такой ор-

ганизации системы прерываний ВУ, запросившее обслуживание, само иден-

тифицирует себя с помощью вектора прерывания – адреса ячейки основной

памяти микроЭВМ, в которой хранится либо первая команда подпрограммы

обслуживания прерывания данного ВУ, либо адрес начала такой подпро-

граммы. Таким образом, процессор, получив вектор прерывания, сразу пере-

23

ключается на выполнение требуемой подпрограммы обработки прерывания.

В микроЭВМ с векторной системой прерывания каждое ВУ должно иметь

собственную подпрограмму обработки прерывания. Различают векторные

системы с интерфейсным и внеинтерфейсным вектором. В первом случае

вектор прерывания формирует контроллер ВУ, запросившего обслуживания,

во втором – контроллер прерываний, общий для всех устройств, работающих

в режиме прерываний (IBM-совместимые персональные компьютеры).

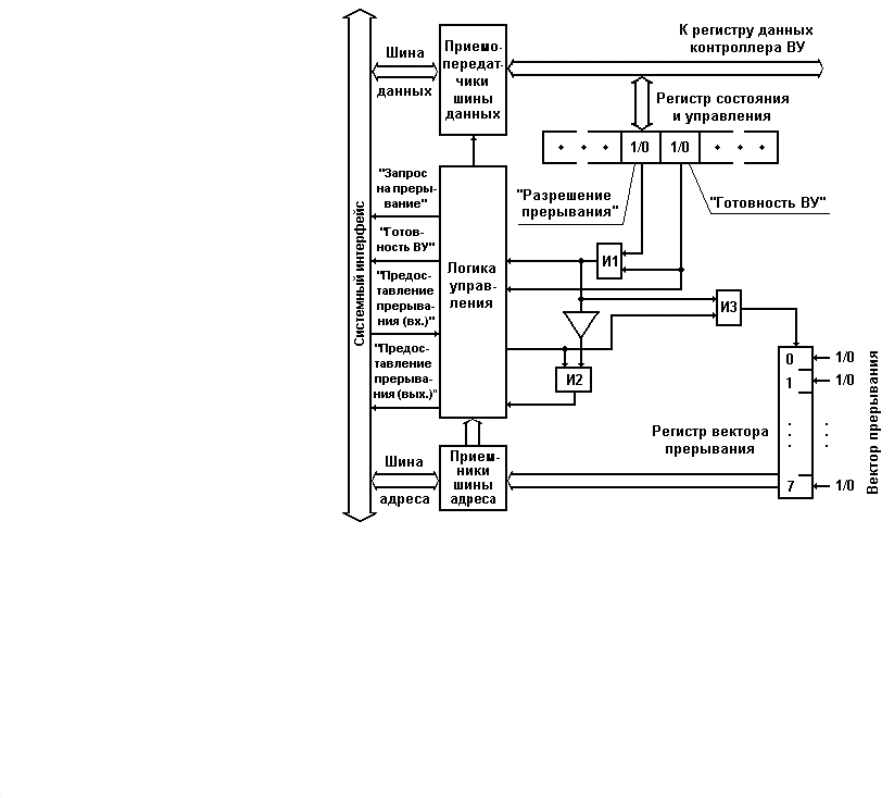

Рассмотрим организацию векторной системы с интерфейсным векто-

ром. Вектор прерывания выдается контроллером не одновременно с запро-

сом на прерывание, а только по разрешению процессора, как это реализовано

в схеме на рис. 14. Это делается для того, чтобы исключить одновременную

выдачу векторов прерывания от нескольких ВУ. В ответ на сигнал контрол-

лера ВУ «Запрос на прерывание» процессор формирует управляющий сигнал

«Предоставление прерывания», который разрешает контроллеру ВУ, запро-

сившему обслуживание, выдачу вектора прерывания в шину адреса систем-

ного интерфейса. Для этого в контроллере используются регистр вектора

прерывания и схема совпадения И3. Регистр вектора прерывания обычно

реализуется с помощью перемычек или переключателей, что позволяет поль-

зователю устанавливать для конкретных ВУ требуемые значения векторов

прерывания.

Рис. 14. Формирование векторов прерывания в контроллере ВУ

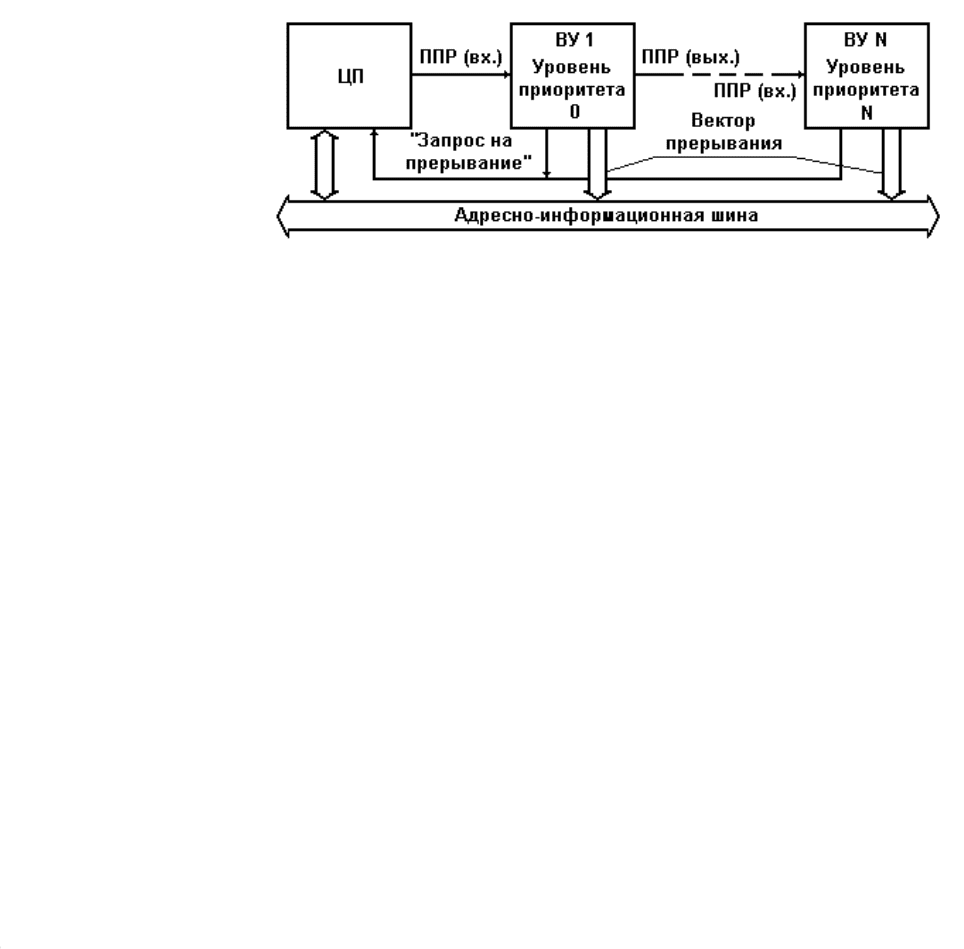

Управляющий сигнал «Предоставление прерывания» формируется в

контроллере ВУ с помощью схемы совпадения И2. Этот сигнал используется

для организации последовательного аппаратного опроса готовности ВУ и

24

реализации тем самым требуемых приоритетов ВУ. Процессор при поступ-

лении в него по общей линии системного интерфейса «Запрос на прерыва-

ние» сигнала прерывания формирует управляющий сигнал «Предоставление

прерывания)», который поступает сначала в контроллер ВУ с наивысшим

приоритетом (рис. 15). Если это устройство не требовало обслуживания, то

его контроллер пропускает сигнал «Предоставление прерывания» на сле-

дующий контроллер, иначе дальнейшее распространение сигнала прекраща-

ется и контроллер выдает вектор прерывания на адресно-информационную

шину.

Аппаратный опрос готовности ВУ производится гораздо быстрее, не-

жели программный. Но если обслуживания запросили одновременно два или

более ВУ, обслуживание менее приоритетных ВУ будет отложено на время

обслуживания более приоритетных, как и в системе прерывания с программ-

ным опросом.

Рис. 15. Реализация приоритетов ВУ в МПС с векторной системой прерываний

с интерфейсным вектором (ППР(вх) – «Предоставление прерывания (входной)»;

«ППР(вых) – «Предоставление прерывания (выходной)

Векторная система с внеинтерфейсным вектором прерывания исполь-

зуется в IBM-совместимых персональных компьютерах. В этих компьютерах

контроллеры внешних устройств не имеют регистров для хранения векторов

прерывания, а для идентификации устройств, запросивших обслуживания,

используется общий для всех ВУ контроллер прерываний типа I8259А.

БИС программируемого контроллера прерываний представляет собой

устройство, реализующее до восьми уровней запросов на прерывания с воз-

можностью программного маскирования и изменения порядка обслуживания

прерываний. За счет каскадного включения БИС ПКП число уровней преры-

вания может быть расширено до 64.

Структурная схема программируемого контроллера прерываний и ра-

бота микросхемы подробно рассмотрены в курсе лекций по дисциплине.

Прямой доступ к памяти. Рассмотрим третий из перечисленных спосо-

бов обмена данными: обмен в режиме прямого доступа к памяти (ПДП). В

25

этом режиме обмен данными между ВУ и основной памятью МПС происхо-

дит без участия процессора. Обменом в режиме ПДП управляет не програм-

ма, выполняемая процессором, а электронные схемы, внешние по отношению

к процессору. Обычно схемы, управляющие обменом в режиме ПДП, разме-

щаются в специальном контроллере, который называется контроллером пря-

мого доступа к памяти. Обмен данными в режиме ПДП позволяет использо-

вать быстродействующие внешние запоминающие устройства, такие, напри-

мер, как накопители на жестких магнитных дисках, поскольку ПДП может

обеспечить время обмена одним байтом данных между памятью и ВЗУ, рав-

ное циклу обращения к памяти.

Для реализации режима прямого доступа к памяти необходимо обеспе-

чить непосредственную связь контроллера ПДП и памяти МПС. Для этой це-

ли можно было бы использовать специально выделенные шины адреса и

данных, связывающие контроллер ПДП с основной памятью. Но такое реше-

ние нельзя признать оптимальным, так как это приведет к значительному ус-

ложнению микроЭВМ в целом, особенно при подключении нескольких ВЗУ.

В целях сокращения количества линий в шинах микроЭВМ контроллер ПДП

подключается к памяти посредством шин адреса и данных системного ин-

терфейса. При этом возникает проблема совместного использования шин

системного интерфейса процессором и контроллером ПДП. Можно выделить

два основных способа ее решения: реализация обмена в режиме ПДП с «за-

хватом цикла» и в режиме ПДП с блокировкой процессора.

Существуют две разновидности прямого доступа к памяти с «захватом

цикла». Наиболее простой способ организации ПДП состоит в том, что для

обмена используются те машинные циклы процессора, в которых он не об-

менивается данными с памятью. В такие циклы контроллер ПДП может об-

мениваться данными с памятью, не мешая работе процессора. Однако возни-

кает необходимость выделения таких циклов, чтобы не произошло временно-

го перекрытия обмена ПДП с операциями обмена, инициируемыми процес-

сором. В некоторых процессорах формируется специальный управляющий

сигнал, указывающий циклы, в которых процессор не обращается к систем-

ному интерфейсу. При использовании других процессоров для выделения та-

ких циклов необходимо применение в контроллерах ПДП специальных се-

лектирующих схем, что усложняет их конструкцию. Применение рассмот-

ренного способа организации ПДП не снижает производительности МПС, но

при этом обмен в режиме ПДП возможен только в случайные моменты вре-

мени одиночными байтами или словами.

Более распространенным является ПДП с «захватом цикла» и принуди-

тельным отключением процессора от шин системного интерфейса. Для реа-

лизации такого режима ПДП системный интерфейс дополняется двумя ли-

ниями для передачи управляющих сигналов «Запрос прямого доступа к па-

мяти» (ЗПДП) и «Предоставление прямого доступа к памяти» (ППДП).

26

Управляющий сигнал ЗПДП формируется контроллером прямого дос-

тупа к памяти. Процессор, получив этот сигнал, приостанавливает выполне-

ние очередной команды, не дожидаясь ее завершения, выдает на системный

интерфейс управляющий сигнал ППДП и отключается от шин системного

интерфейса. С этого момента все шины системного интерфейса управляются

контроллером ПДП. Контроллер ПДП, используя шины системного интер-

фейса, осуществляет обмен одним байтом или словом данных с памятью

МПС и затем, сняв сигнал ЗПДП, возвращает управление системным интер-

фейсом процессору. Как только контроллер ПДП будет готов к обмену сле-

дующим байтом, он вновь «захватывает» цикл процессора и т. д. В проме-

жутках между сигналами ЗПДП процессор продолжает выполнять команды

программы. Тем самым выполнение программы замедляется, но в меньшей

степени, чем при обмене в режиме прерываний.

Применение в МПС обмена данными с ВУ в режиме ПДП всегда тре-

бует предварительной подготовки, а именно: для каждого ВУ необходимо вы-

делить область памяти, используемую при обмене, и указать ее размер, т. е.

количество записываемых в память или читаемых из памяти байт (слов) ин-

формации. Следовательно, контроллер ПДП должен обязательно иметь в

своем составе регистр адреса и счетчик байт (слов). Перед началом обмена с

ВУ в режиме ПДП процессор должен выполнить программу загрузки. Эта

программа обеспечивает запись в указанные регистры контроллера ПДП на-

чального адреса выделенной ВУ памяти и ее размера в байтах или словах в

зависимости от того, какими порциями информации ведется обмен. Сказан-

ное не относится к начальной загрузке программ в память в режиме ПДП. В

этом случае содержимое регистра адреса и счетчика байт слов устанавлива-

ется переключателями или перемычками непосредственно на плате контрол-

лера. В качестве контроллера ПДП в МПС на базе I8086/88 используется

микросхема I8237 (К1810ВТ37). Работа контроллера и принципы его про-

граммирования подробно рассмотрены в курсе лекций по дисциплине.

Задания к разделу 1.

Для закрепления знаний, полученных на лекциях и практических заня-

тиях, предлагается выполнить ряд заданий.

1) Считая, что команда уже находится в очереди, определите число

циклов шины, необходимых для выполнения каждой из следующих команд:

а) PUSH AX

б) CALL NEAR RTR PROC_A

в) CALL FAR RTR PROC_B

г) MOV DATA,AX (четный адрес)

д) MOV DATA,AX (нечетный адрес)

е) OUT 6OH,AX.

27

2) Чему равно минимальное число циклов шины между моментом рас-

познавания запроса прерывания и выборкой первой команды процедуры пре-

рывания?

3) Напишите фрагмент инициализации микросхемы I8251A на асин-

хронную передачу со следующим форматом: 7 информационных бит, 1 сто-

повый бит, бит паритета отсутствует. Множитель скорости передачи равен

64. Четный адрес 8251А равен 008А. Включите во фрагмент приказ, который

выдает сигналы RTS и DTR и разрешает передатчик.

4) Опишите, как микросхему I8254 (таймер) можно использовать для

подсчета входных импульсов в течение временного интервала, управляемого

вторым входом. По окончании всего счета выдается запрос прерывания по

линии IR2, а после каждых 20 подсчитанных импульсов формируется запрос

прерывания по линии IR3. Напишите программу инициализации I8254.

5) Поясните, почему очередь команд улучшает коэффициент использо-

вания процессора в мультипроцессорной системе.

6) Пусть следующие 16-ричные числа представляют короткие вещест-

венные числа:

- CA5B2000 3C630000 4C341200

- Определите десятичные эквиваленты этих чисел.

7) По каким критериям можно судить о «мощности» процессора, о его

«производительности »?

8) Во сколько раз уменьшается длина записи числа при переходе от

двоичной формы представления к шестнадцатеричной?

9) В какой системе счисления представлено число 03С4Н?

10) Какую функцию выполняет счётчик команд IP в микропроцессоре?

11) Какая из трёх шин микропроцессора является однонаправленной?

12) Где хранится программа?

13) Какая разница между программой на машинном языке и програм-

мой, написанной на каком-либо высокоуровневом языке?

14) Что такое код операции?

15) Зачем нужна оперативная память?

16) Что такое кэш-память и для чего она используется в процессорах?

2. НАДЁЖНОСТЬ РАБОТЫ МИКРОПРОЦЕССОРНОГО ВЫЧИСЛИТЕЛЯ

Долговременность и надёжность работы микропроцессорных вычис-

лителей напрямую зависят от способов отладки как устройств, так и про-

грамм. Рассмотрим ряд вопросов, не вошедших в курс лекций.

2.1. Оценка надёжности

В технические требования к аппаратуре часто включаются такие ха-

рактеристики, как среднее время между отказами (СВМО) и показатель го-

28

товности. Выяснение значений параметров надёжности и готовности требует

длительного наблюдения за функционированием системы и регистрации от-

казов; однако существует возможность прогнозировать СВМО системы на

этапе её разработки и вносить в проект изменения, направленные на удовле-

творение технических требований.

Если за коэффициент надёжности некоторого элемента R(t) принять

вероятность его удовлетворительного функционирования в течение заданно-

го периода времени, то коэффициент надёжности большего числа аналогич-

ных элементов R(t) за время t может быть рассчитан по следующей формуле:

R(t)=Кол-во неисправных элем. в момент t / Общее количество элементов

При постоянной интенсивности отказов коэффициент надёжности со

временем экспоненциально убывает Обычно, если оборудование после отка-

зов восстанавливается, используется термин «среднее время между отказами

(СВМО)». Если ремонт оборудования не выполняется, как правило, применя-

ется термин «среднее время до отказа (СВДО)».

2.2. Совершенствование обслуживания систем

Время восстановления работоспособности складывается их несколь-

ких составляющих:

- времени обнаружения ошибки;

- подготовительного времени;

- времени локализации неисправности;

- времени разборки;

- времени замены неисправных элементов;

- времени сборки;

- времени наладки;

- времени проверки работоспособности.

Все эти виды работ должны приниматься во внимание на этапе проек-

тирования оборудования с целью сокращения времени восстановления рабо-

тоспособности и совершенствования тем самым обслуживаемой системы.

Сокращение затрат на замену неисправных элементов достигается за счёт

использования модульного принципа конструирования с применением легко

заменяемых модулей. Времена разборки и сборки в значительной степени

определяются конструкцией корпусных деталей системы, а времена обнару-

жения ошибки, локализации неисправностей и проверки работоспособности

могут быть существенно сокращены при наличии в системе встроенных

средств контроля аппаратного и (или) программного обеспечения.

Известен ряд принципов схемного проектирования, позволяющих

улучшить тестируемость системы:

а) разделение сложных функциональных устройств на меньшие функ-

ционально законченные элементы;

29

б) наличие в составе платы контрольных точек, выведенных на торце-

вые разъёмы;

в) возможность отключения любого логического узла от общей шины;

г) возможность использования внешнего генератора тактовых сигналов;

д) применение колодок для монтажа сложных ИС;

е) возможность доступа с целью контроля ко всем входам и выходам;

ж) возможность начальной установки всех элементов памяти;

з) возможность размыкания любой цепи обратной связи;

и) исключение логической избыточности;

к) исключение применения схем с одним устойчивым состоянием и

асинхронных логических схем;

л) исключение случаев превышения нагрузочной способности.

Для диагностики неисправностей сложных цифровых схем могут быть

применены относительно недорогие средства сигнатурного анализа. Сигна-

турный анализ – это метод контроля, основанный на сжатии данных с ис-

пользованием циклической избыточности; проверочный код вырабатывается

генератором псевдослучайных двоичных последовательностей, который вос-

принимает последовательные битовые оттоки. Получая сигнатуры различных

точек неисправной платы, содержащей цифровое устройство, и сравнивая их

с сигнатурами, полученными с заведомо исправной платы, часто оказывается

возможным локализовать источник неисправности гораздо быстрее, чем с

помощью других видов контрольной аппаратуры. Чтобы пользоваться сигна-

турным анализом, необходимо предусмотреть в устройстве соответствующее

количество легко доступных контрольных точек, а также средства блокиров-

ки шинных формирователей.

2.3. Функции средств отладки

Сроки и качество отладки системы зависят от средств отладки. Чем со-

вершеннее приборы, имеющиеся в распоряжении инженера-разработчика,

тем скорее можно начать отладку аппаратуры и программ и тем быстрее об-

наружить ошибки, локализовать источники, устранение которых обойдется

дороже на более позднем этапе проектирования.

Средства отладки должны:

1) управлять поведением системы или/и ее модели на различных уров-

нях абстрактного представления;

2) собирать информацию о поведении системы или/и ее модели, обра-

батывать и представлять на различных уровнях абстракции;

3) преобразовывать системы, придавать им свойства контролепригод-

ности;

4) моделировать поведение внешней среды проектируемой системы.