Певцов Е.Ф., Смирнов А.Н. Методические указания по выполнению лабораторных работ: Проектирование цифровых схем на основе ПЛИС

Подождите немного. Документ загружается.

31

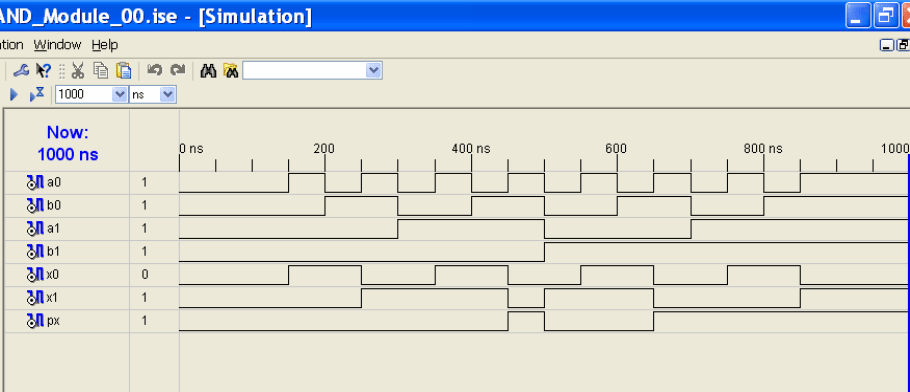

симулятор (Process – Xilinx ISE Simulator – Simulate Behavioral

Model) и в открывшемся окне (см. рис. 18) проанализируйте диа-

граммы входных и выходных сигналов.

Рис.18. Результат работы программы тестирования.

Изучите возможности манипулирования с настройками симуля-

тора. При необходимости, измените исходный код тестирующей

программы и настройки вывода результатов симуляции.

3.9. Выполните разработку схемы сумматора с двумя разрядами и

переносом, другим способом (используя только программный

VHDL-код). Сравните полученную схему с полученной в п.3.4.

Задание 4. Разработка генератора

произвольной кодовой по-

следовательности. В среде ISE разработайте схему, реализую-

щую генератор произвольной кодовой последовательности с так-

товыми сигналами, заданными преподавателем.

4.1. Примите во внимание, что внутри ПЛИС нет собственного ис-

точника тактовых сигналов, поэтому для создания схемы приме-

нить описание счетчиков входных сигналов, задаваемых внешним

тактовым генератором. Любая кодовая последовательность

созда-

ется при помощи комбинирования сигналов счетчика.

4.2. При создании модуля используйте следующие порты: вход-

ной сигнал генератора (clk), входной сигнал сброса (rst) и выход-

ные сигналы в соответствии с требованиями формируемой кодо-

вой последовательности. В некоторых случаях удобно использо-

вать триггеры. Триггер следует вынести в отдельный модуль, и

потом

использовать, как было описано выше. При этом в качест-

32

ве тактового сигнала для него возможно использование не только

сигналов clk, но и сигналов счетчиков.

4.4. Для формирования счетчика необходимо задать внутреннюю

шину, например: cnt : STD_LOGIC_VECTOR (N downto 0);

4.5. Затем в основном модуле следует задать процесс, реализую-

щий счетчик

cnt1: process (clk, rst)

begin

IF rst='1' then

cnt <= "00000";

-- должно быть столько нулей, сколько разрядов у счетчика

elsif clk='1'

and clk'event then

cnt <= cnt + 1;

end IF;

end process;

4.6. Формирование требуемых сигналов кодовой последователь-

ности производится комбинированием с помощью логических

функций различных сигналов счетчика..

Библиографический список

1. http:/www.xilinx.com

2. http:/www.plis.ru

3. Дж. Ф. Уэйкерли Проектирование цифровых устройств.

В 2-х томах. М.: Постмаркет, 2002.

4. Суворова Е.А., Шейнин Ю.Е. Проектирование цифровых

систем на VHDL. – СПб.: БХВ-Петербург, 2003. – 576

с..

5. Бибило П.Н. Основы языка VHDL. – М.: «Солон-Р», 2000. –

200 с.

6. Зотов В.Ю. Проектирование цифровых устройств на основе

ПЛИС фирмы XILINX в САПР WebPACK ISE. – М.: Горячая ли-

ния-Телеком, 2003. – 624 с.

7. Тарасов И.Е. Разработка цифровых устройств на основе

ПЛИС XILINX

®

с применением языка VHDL. М.: Горячая линия-

Телеком, 2005. – 252 с.

8. Перельройзен Е.З. Проектируем на VHDL. - М.: Изд-во

"СОЛОН-Пресс", 2004. - 448 с.

9. Поляков А. К. Языки VHDL и VERILOG в проектировании

цифровой аппаратуры. - М.: Изд-во "СОЛОН-Пресс", 2003. - 320 с.