Расчет и проектирование СБИС. Лекции

Подождите немного. Документ загружается.

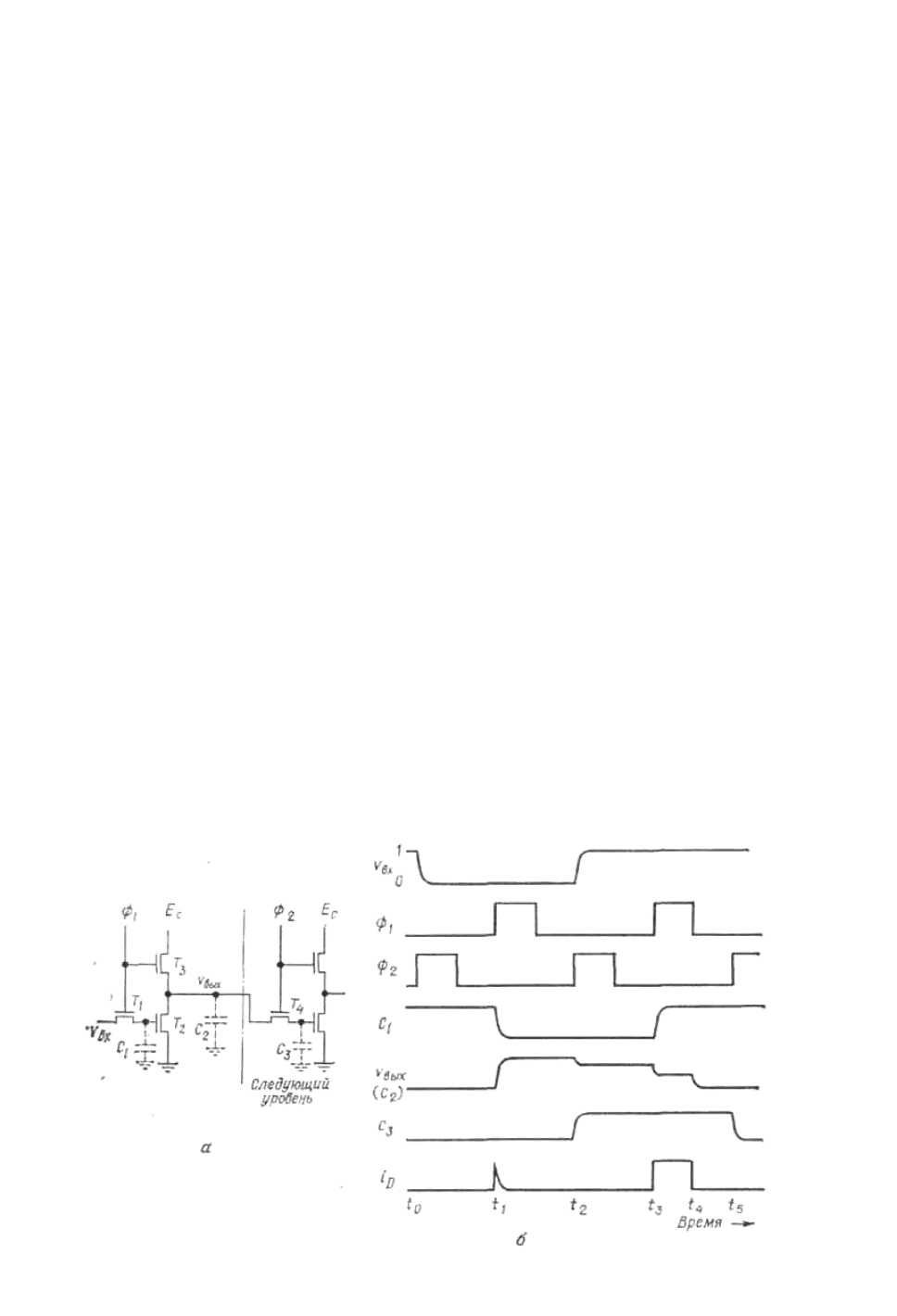

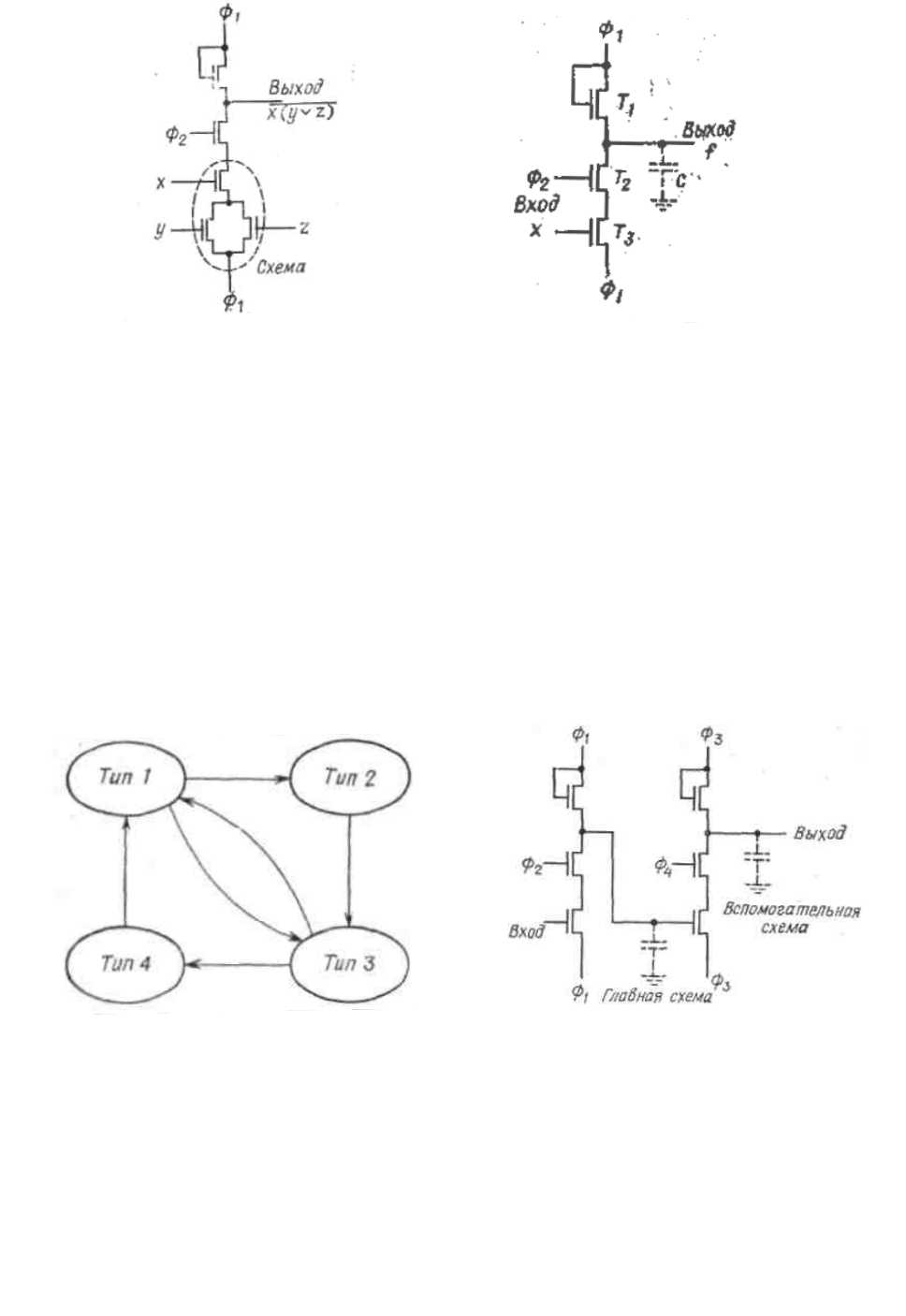

Рис.4.8.4. Двухфазный динамический сдвиговый регистр.

На рис. 4.8.3 показана динамическая МОП-ячейка, реализующая операцию

И-НЕ. Динамические МОП-схемы для других переключательных функций

строятся аналогичным образом. На рис. 4.8.4 приведена схема динамического

сдвигового регистра, в котором паразитные емкости C

1

и С

2

выполняют роль

соответственно главной и вспомогательной частей статического триггера.

Поскольку для динамической МОП-схемы на рис. 4.8.2, а необходимы две

последовательности синхроимпульсов φ

1

и φ

2

, такие схемы называются схемами с

двухфазной синхронизацией (или с 2φ-синхронизацией).

Транзисторы Т

1

и Т

4

(рис. 4.8.2, а) называют передаточными вентилями, так

как их функция заключается в передаче электрического заряда с одной паразитной

емкости на другую. Необходимо отметить, что, если емкость С

3

не будет намного

меньше емкости С

2

, напряжение на С

3

может стать слишком низким, так как

содержащийся на С

2

заряд в момент t

2

должен быть разделен между емкостями

С

2

и С

3

. (Этот процесс носит название распределения заряда.) Однако иногда на

стадии разработки топологии бывает сложно точно задать величины паразитных

емкостей. Кроме того, напряжение, до которого заряжается емкость С

3

, обычно

ниже, чем напряжение на емкости С

2

, так как транзистор Т

4

запирается, когда

разность потенциалов между затвором транзистора Т

4

и емкостью С

3

меньше по-

рогового напряжения, как следует из рис. 4.1.9.

Рассмотрим теперь двухфазные динамические МОП-схемы, значительно

отличающиеся от описанных выше. Двухфазный квазистатический инвертор (рис.

4.8.5) синхронизируется двумя последовательностями синхроимпульсов φ

1

и φ

2

и

снабжен источником питания постоянного тока Е

с

, который отсутствует в схемах на

рис. 4.8.2—4.8.4. Транзистор Т

2

заземлен. Допустим, что в момент t

0

(рис. 4.8.5, б)

входное напряжение U

BX

меняется от высокого уровня (логической 1) до низкого

(логического 0).

Рис. 4.8.5. Двухфазный квазистатический инвертор.

121

В момент t

1

транзисторы Т

2

и Т

3

открываются вследствие воздействия

синхроимпульса φ

1

и паразитная емкость С

1

разряжается через передаточный

вентиль Т

1

, а С

2

заряжается до высокого напряжения, близкого к напряжению

источника питания постоянного тока Е

с

. В момент t

2

передаточный вентиль Т

4

от-

крывается под воздействием синхроимпульса φ

2

, в результате чего

электрический заряд передается с емкости С

2

на емкость С

3

.

Если топология разработана таким образом, что величина С

3

гораздо

меньше С

2

, выходное напряжение U

ВЫХ

при этом переносе заряда не оказывается

существенно меньшим, чем напряжение на С

2

до начала переноса. Допустим, что

входное напряжение увеличивается. В момент t

3

транзисторы Т

1

и Т

3

открываются

благодаря синхроимпульсу φ

1

. В этом случае емкость С

1

заряжается до высокого

напряжения, а напряжение на емкости С

2

определяется соотношением

сопротивлений транзисторов Т

3

и Т

2

. Это напряжение не может быть передано с

емкости С

2

на емкость С

3

, так как передаточный вентиль Т

4

заперт.

(Уменьшение напряжения на С

2

по сравнению с его первоначальным значением в

момент t

1

не играет роли.) Следует заметить, что в период времени между t

33

и t

4

от источника питания на землю через транзисторы Т

2

и Т

3

протекает постоянный

ток. В данном случае не возникает проблемы обеспечения необходимого отношения

между сопротивлениями транзисторов, как в статической МОП-схеме. В момент

t

4

транзистор Т

3

запирается в связи с

Рис. 4.8.6. Квазистатическая дина-

мическая ячейка ИЛИ-НЕ.

Рис. 4.8.7. Квазистатический дина-

мический сдвиговый регистр (один

разряд).

окончанием воздействия синхроимпульса φ

1

в результате емкость С

2

полностью

разряжается через транзистор Т

2

. В момент t

5

транзистор Т

4

открывается

синхроимпульсом φ

2

, так что емкость С

3

разряжается через транзисторы Т

4

и Т

2

на

землю. В результате на выходе схемы появляется напряжение U

ВЫХ

, представляющее

собой инвертированное входное напряжение U

ВХ

. Это же напряжение подается на

емкость С

3

.

Хотя при выполнении описанной логической операции в схеме не течет ток

от синхронизирующего источника питания, однако довольно длительное время,

равное длительности одного из синхроимпульсов (от t

3

до t

4

, а также в течение

короткого времени, начиная с момента t

1

в схеме протекает ток от источника

питания Е

с

на землю.) Таким образом, потребляемая мощность в этой схеме

больше, чем в динамических МОП-схемах, рассмотренных выше, но все-таки

значительно меньше, чем в статических МОП-схемах.

122

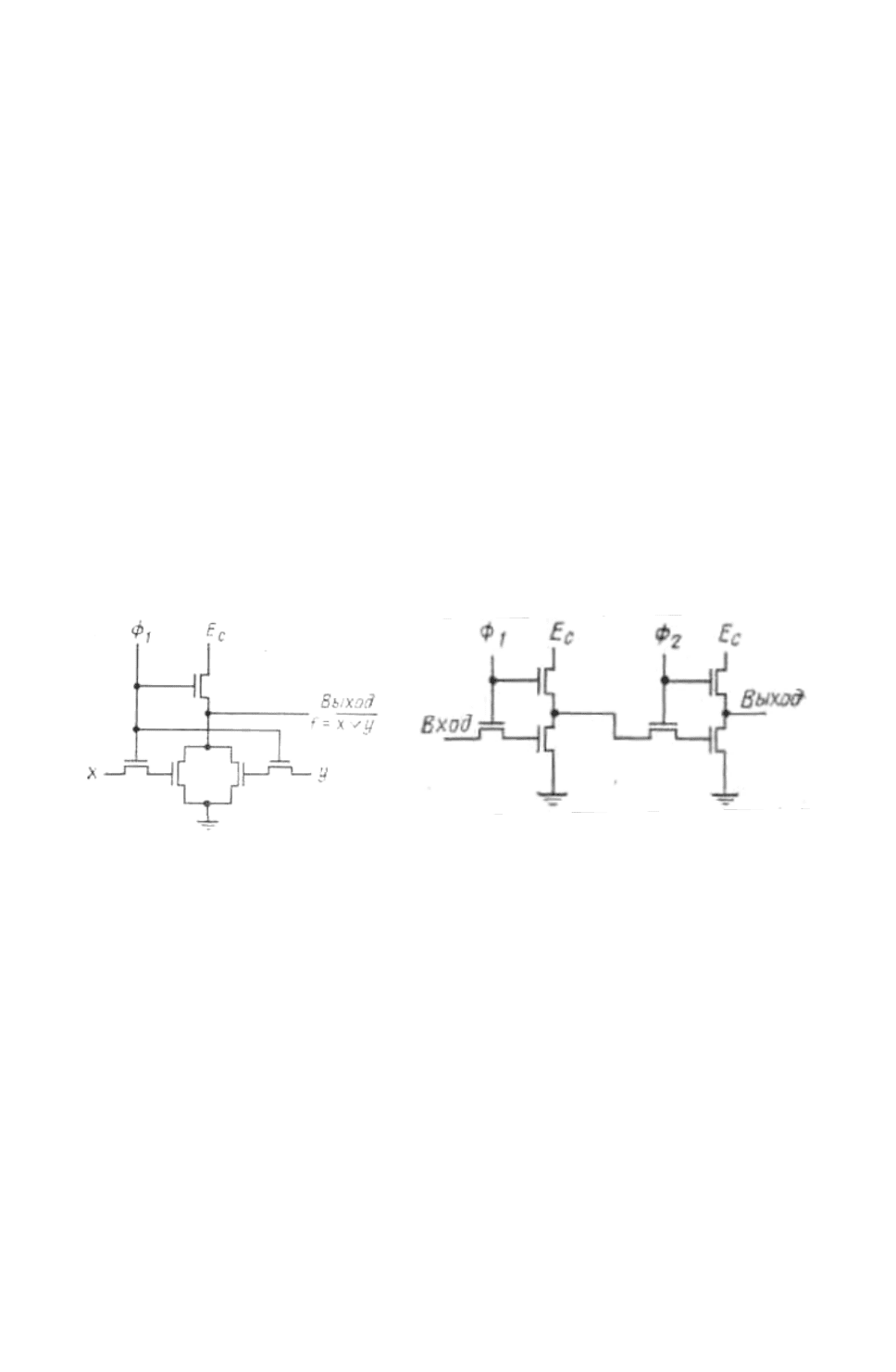

На рис. 4.8.6—4.8.8 показаны квазистатические динамические МОП-

схемы, представляющие собой соответственно элемент ИЛИ-НЕ, разряд

Рис. 4.8.8. Квазистатический динамический SR-фиксатор.

сдвигового регистра и фиксатор SR. В то время как для каждого разряда

сдвигового регистра на статических МОП-схемах требуется триггер, для

устройства, приведенного на рис. 4.8.7, он не нужен.

Квазистатические схемы, приведенные на рис. 4.8.5—4.8.8, хотя и

потребляют большую мощность, обладают следующими преимуществами по

сравнению с динамическими схемами, приведенными на рис. 4.8.2—4.8.4.

Рис. 4.8.9. Квазистатическая динамическая схема, реализующая сложную

логическую функцию.

Упрощается синхронизирующий источник питания, так как он соединен только с за-

творами полевых МОП-транзисторов, практически не потребляющих мощность, в

то время как в динамических МОП-схемах синхронизирующий источник питания,

размещаемый обычно на том же кристалле, должен содержать очень мощные

транзисторы, обеспечивающие большие токи включения и выключения для всех

МОП-ячеек. Другим достоинством этих схем является возможность реализации

сложных логических функций с помощью только одного уровня синхронизации

φ

1

(рис. 4.8.9). В схемах на рис. 4.8.5, а и на рис. 4.8.6 только одна ячейка,

состоящая из транзисторов Т

1

, Т

2

и Т

3

и управляемая последовательностью

синхроимпульсов φ

1

, соединена с передаточным вентилем Т

4

, управляемым

последовательностью синхроимпульсов φ

1

. А на рис. 4.8.9 показано, что для

реализации сложной логической функции может быть сформирована небольшая

123

схема из нескольких МОП-ячеек, каждая из которых управляется

синхроимпульсами φ

1

и соединена с передаточным вентилем, управляемым

синхроимпульсами φ

2

. Заметьте, что здесь не требуется наличия передаточных

вентилей между МОП-ячейками, составляющими эту функциональную часть схемы,

которые необходимы в динамических схемах. В этом случае небольшая схема из

МОП-ячеек работает как статическая МОП-схема в течение действия

синхроимпульса φ

1

(В отличие, от динамических схем здесь не обязательно

производится предварительный заряд паразитных емкостей при подаче

синхроимпульсов.) Следовательно, для каждой МОП-ячейки должна быть

обеспечена большая величина отношения между сопротивлениями нагрузочного и

активного транзисторов. По этой причине схемы, представленные на рис. 4.8.5-

4.8.9, называют квазистатическими, хотя, как отмечено в описании рис. 4.8.5, в

них не возникает проблемы величины отношения сопротивлений транзисторов

(за исключением-схемы на рис. 4.8.9). Таким образом, в используемой

терминологии существует некоторое противоречие.

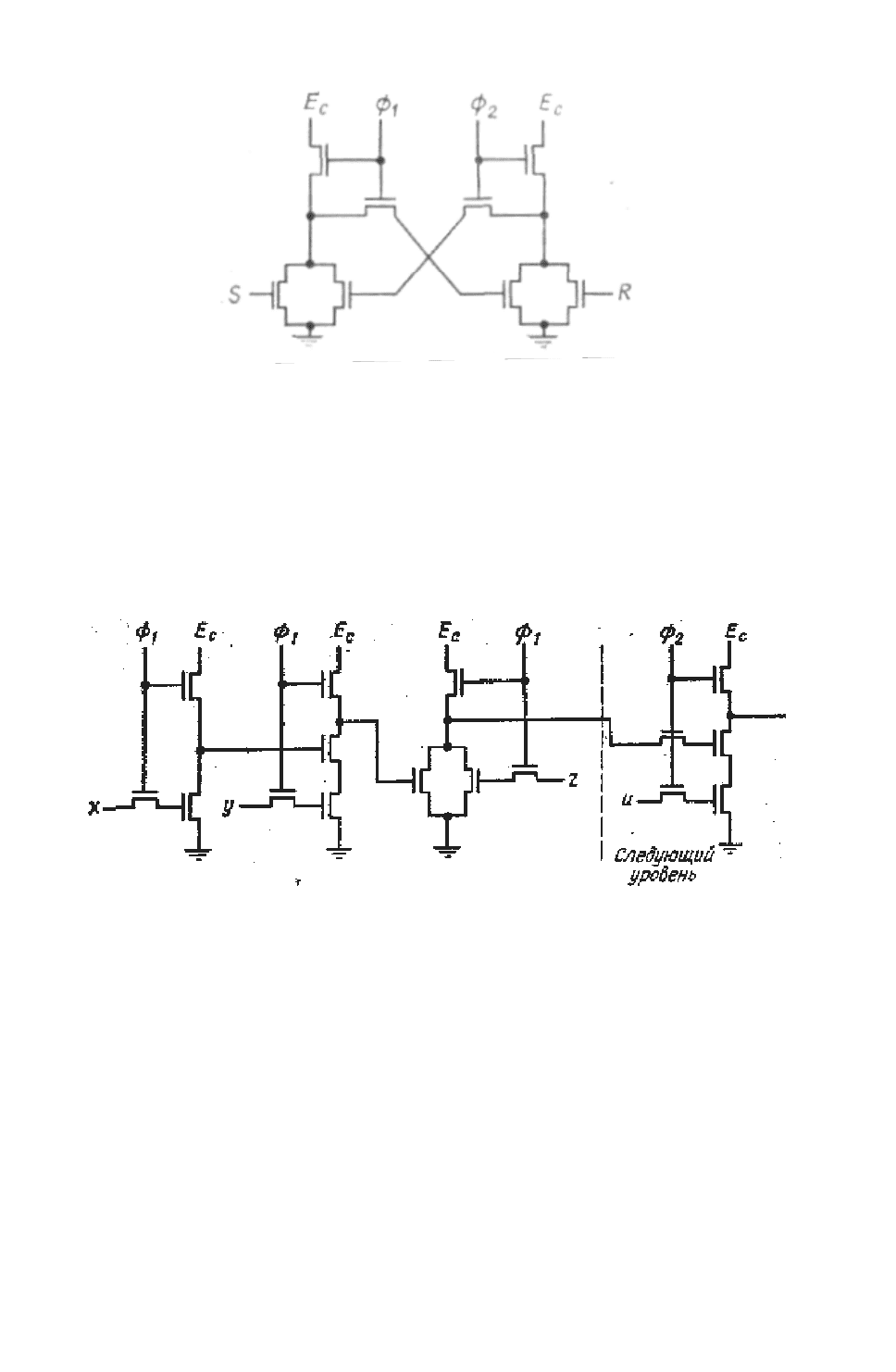

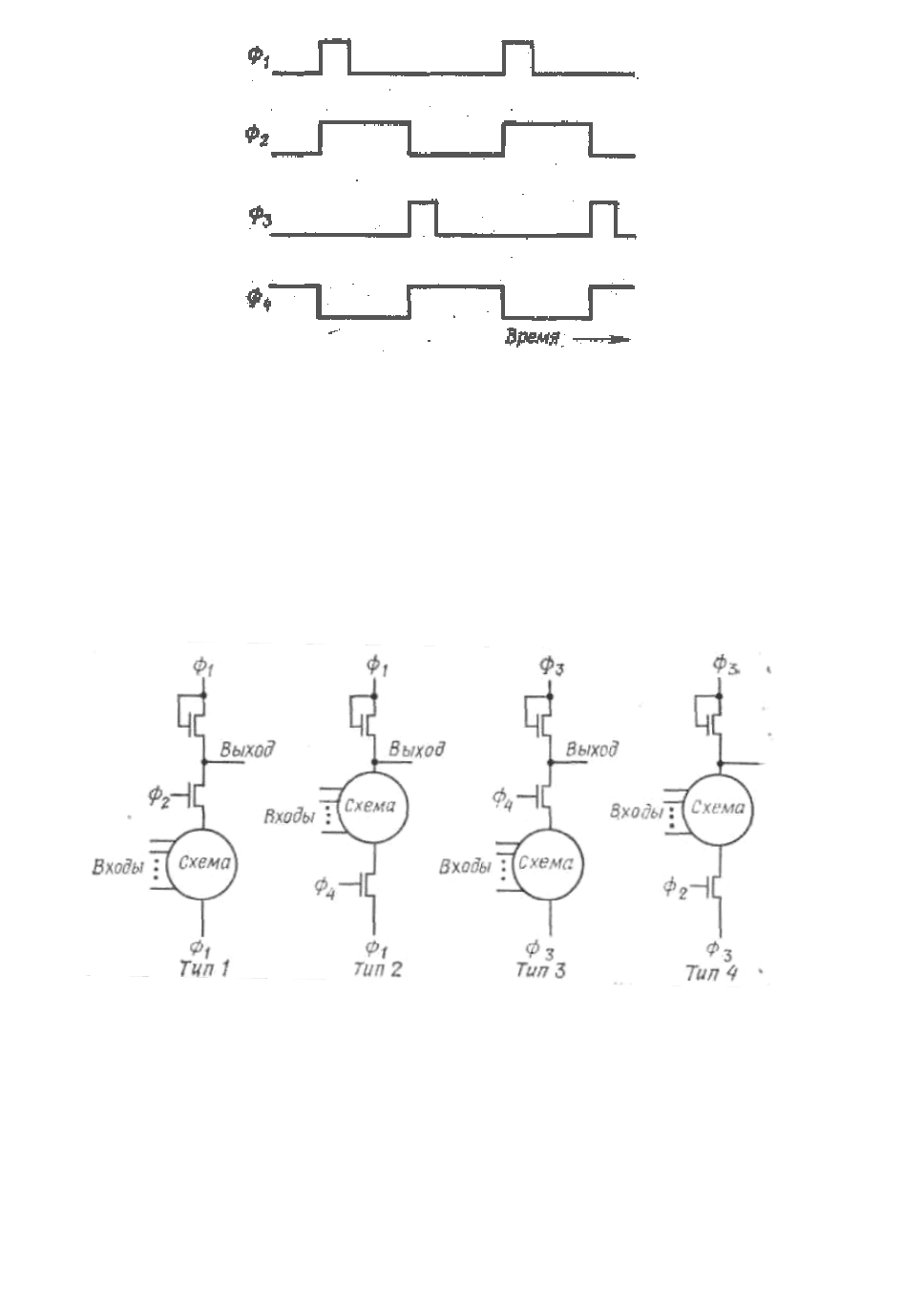

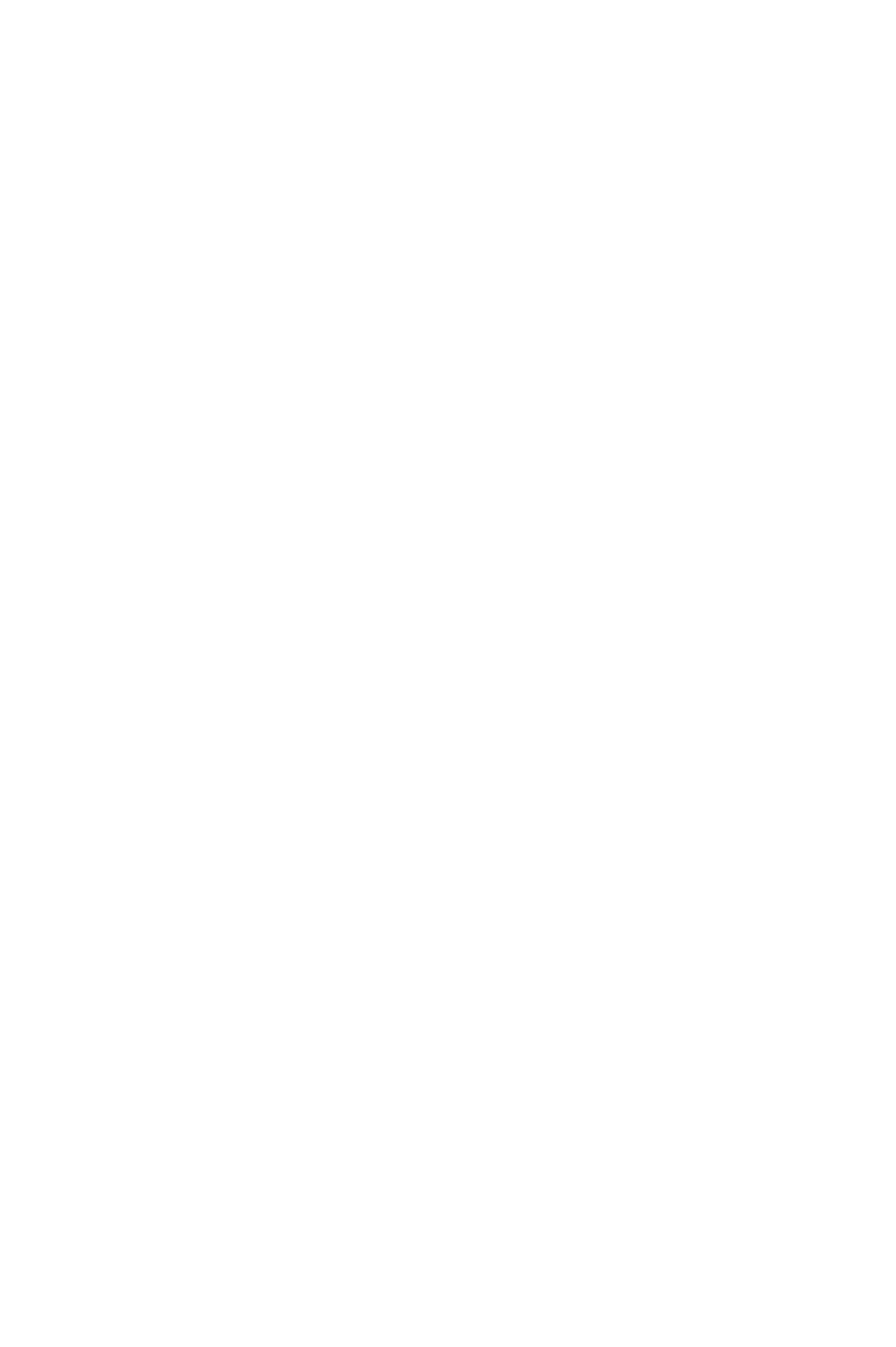

Четырехфазные динамические МОП-схемы

Рассмотрим теперь динамические МОП-схемы с четырехфазной

синхронизацией, т. е. схемы, в которых используются четыре

последовательности синхроимпульсов φ

1

, φ

2

, φ3 и φ

4

(рис. 4.8.10). (Заметьте, что

сигнал φ

4

является инверсным по отношению к сигналу φ

2

.) Объединяя их попарно в

различные комбинации (две комбинации не используются), можно получить

четыре различных типа МОП-ячеек (рис. 4.8.11). Каждый круг обозначает схему,

состоящую из МОП-транзисторов. На рис. 4.8.12 показан пример МОП-ячейки

первого типа, в котором схема обведена штриховой линией. Выходная функция

каждой МОП-ячейки может быть выведена, как это делалось выше. Например,

выходная функция ячейки, приведенной на рис. 4.8.12, имеет вид )( zyx ∨ .

Рассмотрим, как работают такие схемы, на простом примере. На рис. 4.8.13

приведена схема инвертора, построенного на МОП-ячейке первого типа. Когда на

схему поступает синхроимпульс (рис. 4.8.10), транзистор Т

1

открывается и

паразитная емкость С заряжается до высокого положительного напряжения

синхронизирующего источника питания. Во время этого периода заряда и после него

на схему подается синхроимпульс φ

2

. Он обеспечивает открытое состояние

транзистора Т

2

. Тогда, если входное напряжение х является высоким, транзистор Т

3

открывается и емкость С разряжается, что приводит к низкому уровню

выходного напряжения. Если на вход подается низкое напряжение, транзистор Т

3

заперт и на емкости С сохраняется электрический заряд, создающий высокое

напряжение на выходе.

Таким образом, выходное напряжение f является высоким или низким в

зависимости от того, является низким или высоким входное напряжение х.

Следовательно, реализуется функция xf = , и ячейка работает как инвертор.

Другие типы МОП-ячеек выполняют логические операции аналогичным образом.

124

Рис. 4.8.10. Четырёхфазная синхронизация

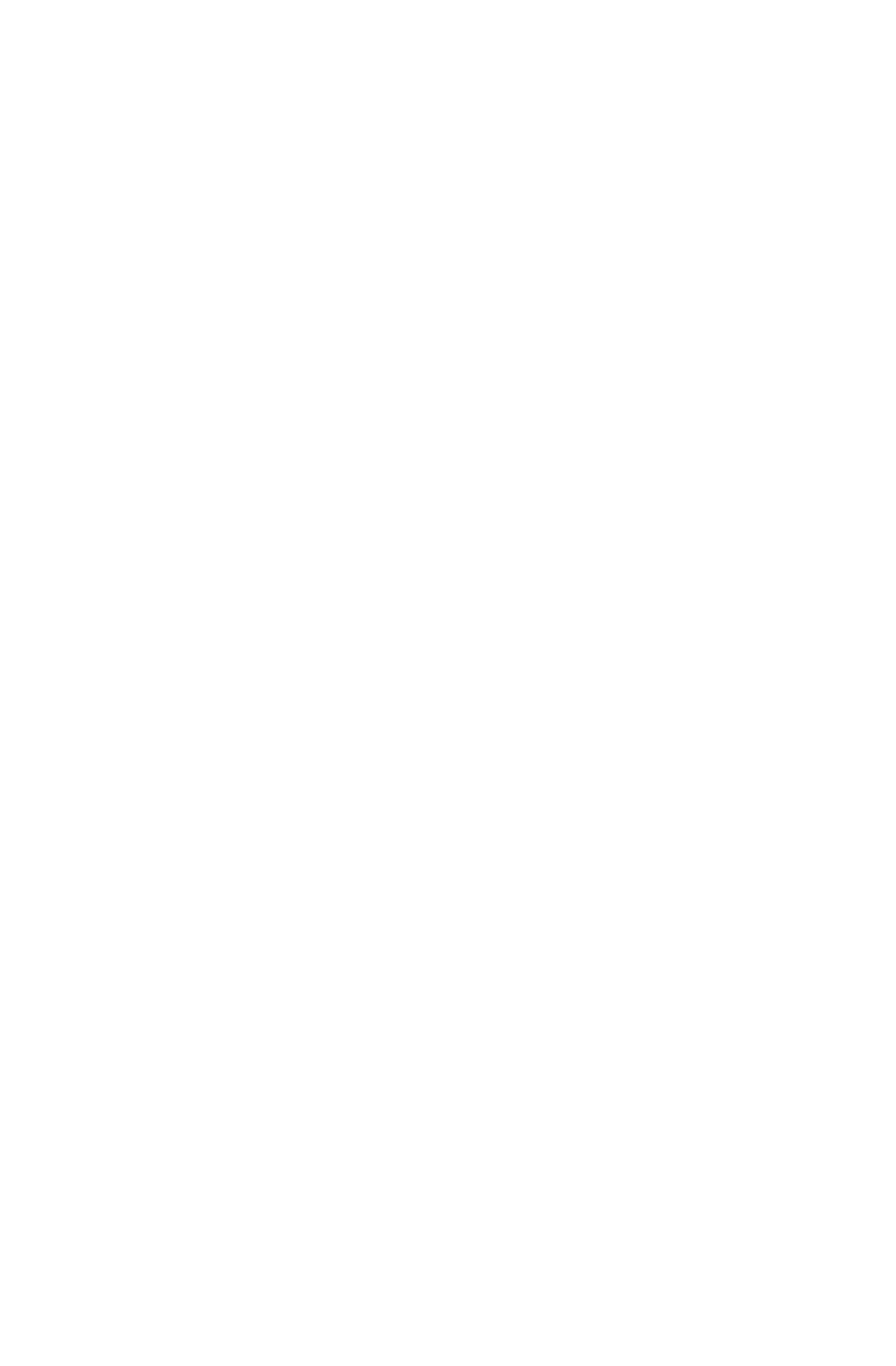

Вся схема строится путем соединения этих различных типов МОП-ячеек. При этом

выход ячейки первого типа может быть подан на вход ячейки второго типа,

выход ячейки второго типа может быть подан на вход ячейки третьего типа, а

выход ячейки третьего типа может быть подан на вход ячейки четвертого типа.

Выход ячейки четвертого типа в свою очередь может быть подан на вход ячейки

первого типа.

Выход ячейки первого типа может быть подан на вход ячейки третьего типа, а

выход ячейки третьего типа — на вход первого. Однако ячейки второго и

четвертого типов не могут быть соединены друг с другом. Кроме того, ячейка

любого типа не может быть соединена с ячейкой того же типа. Соединения,

разрешенные к использованию, показаны на рис. 4.8.14. Примером

четырехфазной динамической МОП-схемы является сдвиговый регистр (рис.

4.8.15).Получение необходимого количества разрядов в регистре обеспечивается

соединением соответствующего числа схем, реализующих один разряд, так как

соединение ячеек первого и третьего типов разрешено (рис. 4.8.4).

125

Рис. 4.8.12. Пример МОП-ячейки 1-го типа.

Рис. 4.8.13. Инвертор

В четырехфазных динамических МОП-схемах не возникает проблем,

связанных с передаточными вентилями, как в двухфазных динамических МОП-

схемах, так как эти вентили не используются. Вместе с тем в этих схемах требуется

большее количество соединений, обеспечивающих подачу синхроимпульсов, из-за

большего количества фаз синхронизации, что увеличивает топологию схемы и

делает ее более громоздкой (в несколько раз больше по сравнению с

двухфазными динамическими схемами). В результате предпочтение, как правило,

отдается двухфазным динамическим схемам, за исключением особых случаев.

Рис.4.8.14. Допустимые соединения

различных типов МОП-ячеек, показанных

на рис. 4.8.11.

Рис. 4.8.13. Инвертор

Имеются и другие варианты реализации четырехфазных динамических

МОП-схем. Например, существует аналог двухфазных квазистатических МОП-

схем, использующий и синхронизирующий источник питания, и источник

питания постоянного тока.

126

127

Существуют и другие модификации динамических МОП-схем с различным

числом фаз синхронизации (например, одной фазой, как в схеме на рис. У.4.8.11,

тремя или шестью фазами, хотя последние схемы не получили широкого

распространения), с перекрывающимися (как φ

1

и φ

2

на рис. 4.8.10) или непере-

крывающимися (как φ

1

и φ

2

на рис. 4.8.2) синхроимпульсами разных фаз, а также

соединениями различных конфигураций.

Свойства динамических МОП-схем

Как видно из вышеприведенных примеров, в динамических МОП-схемах

логические величины 1 и 0 представляются соответственно наличием или

отсутствием заряда на паразитной емкости при поступлении на схему

синхронизирующего импульса, во время действия которого через МОП-

транзисторы не протекает ток от источника питания на землю, за исключением

очень-короткого периода. Синхроимпульсы подаются на все МОП ячейки. В

противоположность этому в статических МОП-схемах логические величины 1 и 0

представляются наличием или отсутствием тока от источника питания на землю

через активные МОП-транзисторы. Паразитные же емкости не играют никакой

роли в их представлении, хотя и влияют на быстродействие схем.

Синхроимпульсы подаются лишь на некоторые ячейки статической МОП-схемы для

синхронизации распространений сигналов по различным путям внутри ячеек.

Использование синхроимпульсов в динамических МОП-схемах позволяет

обойтись без нагрузочных транзисторов, которые являются необходимым

элементом статических МОП-схем и занимают значительную площадь кристалла

(хотя имеются и исключения, например, рис. 4.8.9), в то время как для подводки

синхросигналов достаточно небольшого увеличения площади для выполнения

соответствующих соединений. Таким образом, динамические МОП-схемы являются

более компактными. Быстродействие динамических МОП-схем определяется

частотой синхронизации, которая в свою очередь зависит от скорости заряда и

разряда паразитных емкостей. Если паразитные емкости малы, времена заряда и

разряда невелики и можно увеличить частоту синхронизации, повышая тем самым

скорость выполнения операций. Однако использование синхронизации ограничи-

вает быстродействие динамических схем по сравнению со статическими, поскольку

величина периода синхронизации должна быть выбрана такой, чтобы могло быть

завершено срабатывание самой медленно действующей МОП-ячейки.

Потребляемая мощность в динамических МОП-схемах гораздо меньше, чем в

статических, так как ток в них протекает лишь очень короткое время в течение

длительности синхроимпульсов. Все эти преимущества достигаются за счет

синхросигналов.

Другие вопросы, относящиеся к проектированию динамических схем

Логическое проектирование динамических схем по существу ничем не

отличается от проектирования статических схем. Другими словами, логические

схемы, полученные с использованием процедур, описанных в разд. 4.2 и 4.4, могут

быть легко преобразованы в динамические МОП-схемы. Причем в этом случае

128

отсутствуют столь жесткие ограничения на число последовательно (или

параллельно) соединяемых МОП-транзисторов, как для статических схем, так как

нет необходимости обеспечивать высокое отношение сопротивлений активных и

нагрузочных транзисторов (за исключением схем, аналогичных изображенной на

рис. 4.8.9).

Таким образом, расширяются возможности произвольного соединения

большего количества транзисторов, что позволяет реализовать с помощью одной

МОП-ячейки более сложные переключательные функции. Однако следует иметь в.

виду, что попытка реализовать слишком сложные функции приводит к

чрезмерному усложнению топологии из-за большого количества соединений с

генератором синхросигналов, а значительное число паразитных емкостей и

сопротивлений транзисторов значительно понизит быстродействие схемы. На

практике в любой ветви схемы может быть последовательно соединено не более

четырех транзисторов для обеспечения достаточно высокого быстродействия и не

более десяти, если требования к быстродействию не столь жесткие. Количество

параллельно соединяемых транзисторов ограничивается десятью. Вместе с тем

общее число транзисторов в любой ячейке, по-видимому, не должно превышать

десяти. (С этой точки зрения использование процедуры 4.2.1 более эффективно

для проектирования динамических схем, чем статических, так как применение этой

процедуры часто приводит к получению сложных конфигураций некоторых ячеек.)

Реализация динамических схем на МОП-структурах возможна потому, что

входы МОП-ячеек представляют собой почти чисто емкостные нагрузки.

(Необходимо отметить, что значения входных сопротивлений весьма высоки— ~10

14

Ом.) В этом отношении они сильно отличаются от биполярных логических

элементов, поскольку входные сопротивления биполярных транзисторов очень

малы. МОП-транзисторы служат лишь для заряда и разряда паразитных

емкостей, и при их проектировании не возникает проблемы высокого отношения

сопротивлений для обеспечения большого перепада напряжения (за исключением

схемы на рис. 4.8.9), как в статических МОП-схемах. Следовательно, МОП-

транзисторы могут иметь настолько малые размеры, насколько позволяет

геометрия схемы. Вместе с тем времена заряда и разряда непредсказуемы. (Они

различны для паразитных емкостей, расположенных в разных частях кристалла.)

Это делает необходимым использование генератора синхросигналов, что приводит к

появлению большого количества соединений с ним.

Длинные соединительные проводники обычно нежелательны, так как они

создают большие паразитные емкости. Поэтому предпочтение отдают

модульным структурам. Доля площади, занятой соединениями, из-за присутствия

соединений с синхрогенератором в динамических схемах выше, чем

приведенная в табл. 4.2.1 для статических схем. Уменьшив число МОП-ячеек (с

помощью процедур, аналогичных процедуре 4.2.1), можно не только снизить

потребляемую мощность, но и сократить размеры площади за счет исключения

многих линий подводки синхросигналов и заземления, особенно если число фаз

синхронизации велико.

Выбор частоты синхронизации тесно связан с временами заряда и разрядах

паразитных емкостей. Поскольку электрические заряды должны сохраняться на

паразитных емкостях до тех пор, пока они не будут восприняты МОП-ячейками

129

следующих уровней, частота синхронизации не может быть слишком низкой. В

противном случае имеющийся на паразитной емкости электрический заряд может

разрядиться на землю, так как сопротивление полевых МОП-транзисторов не

является бесконечным, даже когда они заперты. Если частота синхронизации

слишком высока, то за один цикл синхронизации паразитные емкости либо не

будут успевать заряжаться до высокого напряжения, либо, зарядившись, не будут

успевать разряжаться. Другими словами, нормально работать МОП-схема не

будет. При этом с увеличением частоты синхронизации растет и потребляемая

мощность. Точнее говоря, величина потребляемой мощности прямо

пропорциональна произведению

CV

2

f,

где С — паразитная емкость, V—напряжение синхронизирующего источника

питания Е

с

, f — частота синхронизации. Кроме того, при подаче тактовых

импульсов, принадлежащих разным фазам синхронизации, на разные МОП-ячейки

схемы первоначально заданный сдвиг по времени между ними может измениться

из-за того, что соединительные линии отличаются временем задержки. Очевидно,

что с увеличением частоты синхронизации чувствительность схемы к согласованию

во времени возрастает.

В заключение следует заметить, что, несмотря на сложность разработки

топологии, связанной с высокой чувствительностью схем к величинам

паразитных емкостей и большим количеством соединительных линий для подачи

синхроимпульсов, динамические МОП-схемы используются — зачастую

одновременно со статическими схемами — в тех случаях, когда потребляемая

схемой мощность должна быть невысокой.

5. АРХИТЕКТУРА СБИС

5.1 Классификация архитектуры СБИС

• Классификация архитектуры СБИС

Микроэлектроника в своем развитии прошла ряд этапов, каждый из которых

можно охарактеризовать преобладающим архитектурным типом пли

сочетанием нескольких архитектурных типов производимых интегральных

схем. Мы считаем возможным и целесообразным выделить следующие

архитектурные типы ИС:

1) стандартные ИС, СИС и БИС, в том числе БИС полупроводниковой памяти;

2) микропроцессорные комплекты БИС;

3) полузаказные БИС на матрицах логических ячеек;

4) полузаказные БИС на основе ячеек, выполняющих функции стандартных

БИС и ИС;

5) заказные (специализированные) БИС;

6) субсистемы на целой кремниевой пластине;

7) трехмерные ИС.

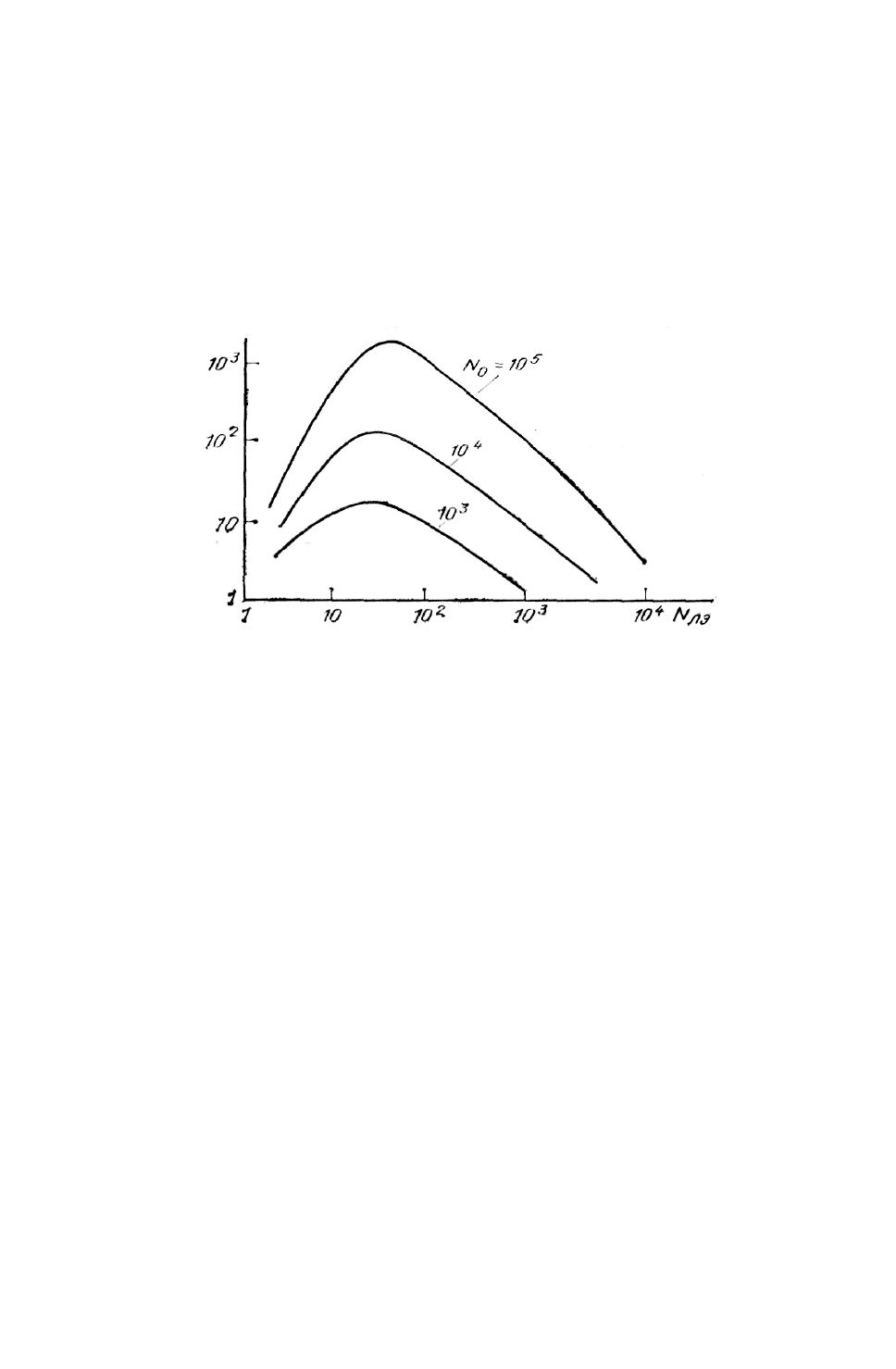

Появление каждого архитектурного типа БИС вызвано необходимостью

разрешения серьезного внутреннего противоречия, возникающего в связи с

неизбежным ростом степени интеграции ИС. Это противоречие заключается в

росте номенклатуры и снижении повторяемости ИС в аппаратуре с ростом

степени интеграции БИС. Интегральная схема высокой степени интеграции

неизбежно становится специализированной, теряет свойства универсальности.

Число типов ИС, необходимых для реализации системы с заданным числом

логических вентилей, по мере роста степени интеграции проходит через

максимум (рис. 5.1.1.).

рис. 5.1.1. Рост номенклатуры (числа функционально различных типов) БИС по мере

увеличения их степени интеграции

N

ЛЭ

, N

0

- общее число логических элементов в

устройстве ЭВМ.

Число выводов БИС возрастает по степенному закону, достигая значений

порядка 10

2

—10

3

. Поскольку аппаратура может быть изготовлена только при

наличии всей номенклатуры БИС одновременно, возникают сложные

проблемы снижения затрат времени на проектирование БИС, изготовление

фотошаблонов и другого специализированного инструмента, изготовление

измерительных и испытательных средств, опытных партий и на организацию

серийного производства БИС. Эти важные проблемы микроэлектроники стоят

того, чтобы на них остановиться подробнее.

•

Стандартные ИМС

Первые два этапа развития микроэлектроники, когда создавались стандартные

ИС и микропроцессорные комплекты БИС, можно назвать ее «золотым веком».

Стандартные ИС и БИС памяти на биполярных транзисторах развивались в

схемотехнике транзисторно-транзисторной логики (ТТЛ), транзисторно-

транзисторной логики с диодами Шоттки (ТТШЛ), эмиттерно-связанной

логики (ЭСЛ), инжекционной логики (И

2

Л). В состав каждого комплекта

включается до 150 типов ИС, выполняющих стандартные логические функции

триггеров, сумматоров, регистров хранения и сдвига, счетчиков, декодеров,

аналого-цифровых и цифро-аналоговых преобразователей, не говоря уже о

стандартных логических вентилях с различным числом входов и нагрузочной

130