Расчет и проектирование СБИС. Лекции

Подождите немного. Документ загружается.

151

7 ПРОЕКТИРОВАНИЕ СБИС.

7.1 Виды проектирования СБИС.

7.1.1 Разработка технологического задания. Функциональное

и логическое проектирование.

При разработке цифровой системы, прежде всего, необходимо определить ее

характеристики. Этот процесс называется этапом составления технических условий.

Затем система разбивается на субблоки и регистры. Тем самым выполняется

функциональное проектирование, в ходе которого определяются функциональные

взаимосвязи между субблоками и регистрами системы. Наилучшим образом

вычислительные системы могут разрабатываться на базе регистров.

Проектирование их на уровнях выше или ниже уровня регистров затруднительно.

Под архитектурой обычно понимают результаты разработки технических

условий и функционального проектирования, но в нее часто включают и часть

результатов следующего этапа разработки, т.е. логического проектирования. Затем

выполняется логическое проектирование схем, которые составляют субблоки и

регистры.

Из всех этапов проектирования составление технического задания,

функциональное и логическое проектирование пока являются наиболее трудно

поддающимися автоматизации с помощью ЭВМ вследствие их сложности. Поэтому

они выполняются в основном вручную. Хотя в прошлом предпринимались попытки

разработки программ автоматизации логического проектирования, результаты были

неутешительными, кроме тех случаев, когда короткий срок проектирования был

более важен, чем размер схемы. Например, для логических схем, разработанных с

помощью программы ALERT, в среднем требовалось на 160% больше вентилей,

чем для таких же схем, разработанных вручную. Однако при очень высокой

степени интеграции положение может измениться, поскольку при ручном

проектировании по мере увеличения степени интеграции срок разработки также

увеличивается и выходит за разумные пределы, логическое проектирование

поглощает очень большую часть времени разработки БИС профессиональными

разработчиками, которые контролируют разработку лишь наиболее сложных слоев

топологии.. Кроме того, различие в результатах между ручным и

автоматизированным проектированием уменьшается вследствие того, что

результаты автоматизированного проектирования улучшаются при интерактивном

взаимодействии с разработчиком.

7.1.2 Проектирование топологии.

Размещение нерегулярных логических схем на кристалле является наиболее

длительным этапом всего цикла проектирования кристалла БИС/СБИС. Такое

размещение обычно выполняется вручную.

152

Размещение нерегулярных логических схем на кристалле является наиболее

длительным этапом всего цикла проектирования кристалла БИС/СБИС. Такое

размещение обычно выполняется вручную.

Размещение и трассировка

По завершении проектирования интегральные схемы должны размещаться

на печатной плате. При этом межсоединения кристаллов ИС следует выполнять

таким образом, чтобы минимизировать полную площадь платы и обеспечить

максимальное быстродействие схемы. (Если некоторое критическое соединение

получается слишком длинным, то быстродействие всей схемы может снизиться.

Например, если время переключения каждого вентиля составляет 4 не, то

максимальная длина каждого межсоединения, как правило, не должна превышать

нескольких сантиметров.) Задача размещения модулей ИС очень важна, так как при

нерациональном размещении ИС нельзя осуществить наилучшую трассировку (т.

е. если ИС с множеством соединений между ними удалены друг от друга, то эти

межсоединения получаются длинными, занимая большую площадь платы и

увеличивая время распространения сигнала). Задачу размещения можно

наилучшим образом решить либо посредством визуальной оценки разных вариантов

размещения разработчиком, либо с помощью высокоинтерактивных программ

автоматизации проектирования.

Решение задачи трассировки необходимо автоматизировать с помощью

специальных программ, потому что для современных цифровых систем

характерно огромное количество соединений как внутри ИС, так и между

ними, что делает не целесообразным решение этой задачи вручную. К

настоящему времени разработано множество процедур трассировки. Ниже

приводятся типичные методы, которые можно использовать для прокладки

соединений между ИС на печатной плате.

Методы автоматизации проектирования для размещения компонентов и

трассировки соединений внутри кристаллов ИС при полузаказном

проектировании ИС, по существу являются теми нее (или аналогичными), что и

методы, которые обсуждаются в данном случае. (Вследствие того, что задача

минимизации площади является более важной для кристаллов ИС, чем для

печатных плат, при конструировании плат трассировка вручную обычно

сочетается с использованием программ автоматизации проектирования, в

которых реализованы рассматриваемые здесь методы проектирования

кристаллов.)

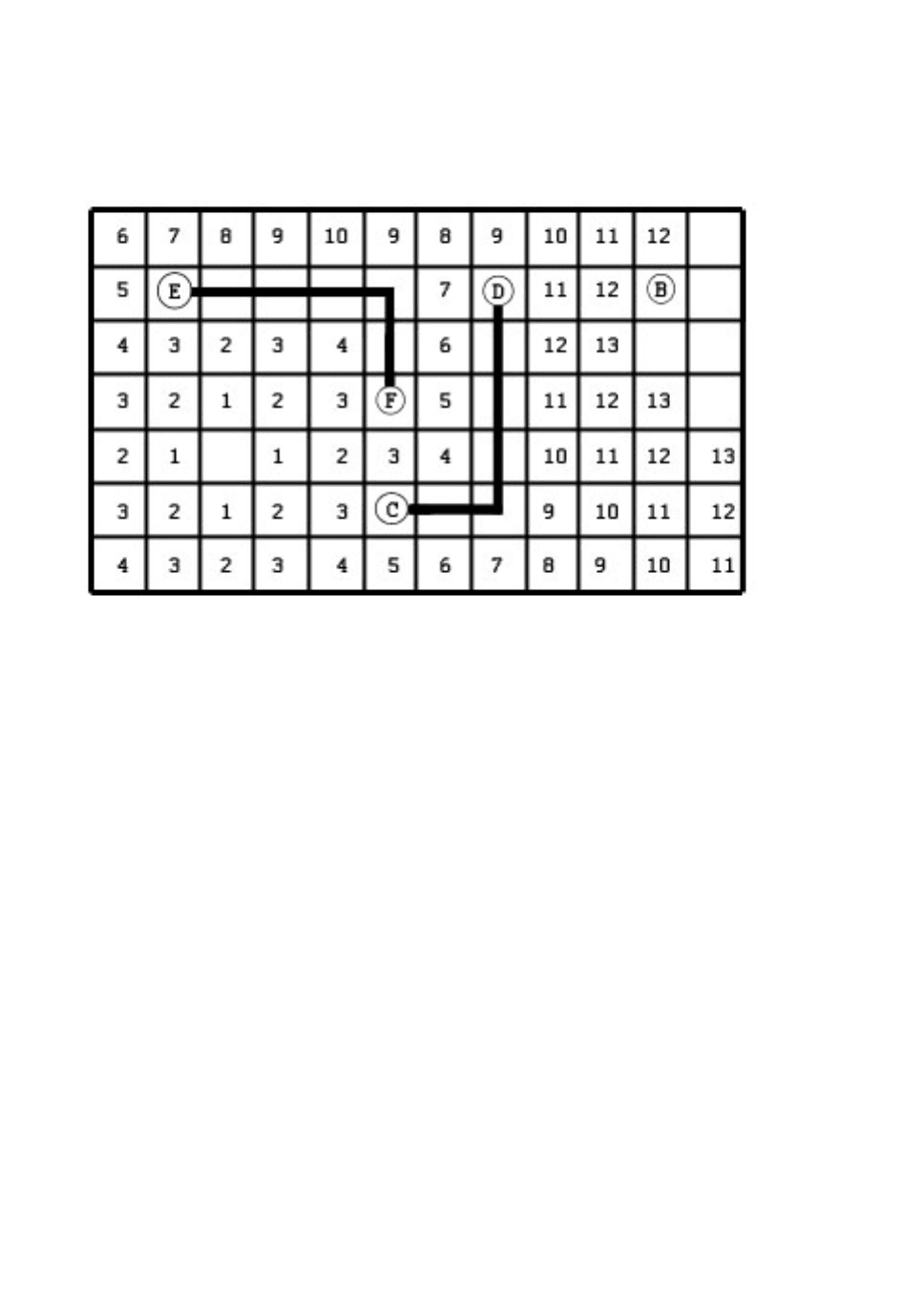

Процедура 7.1.2.1 Метод обхода лабиринта

Предположим, что требуется соединить две точки А и В на печатной плате

(или на кристалле) после того, как соединения между парами точек С, D и F, Е

уже выполнены, как показано на рисунке 7.1. Для этого вся площадь, платы

разбивается на одинаковые прямоугольники (или квадраты), каждому свобод-

ному прямоугольнику, начиная от А и кончая В, сопоставляется число, которое

равно расстоянию данного прямоугольника от точки А, выраженному числом

прямоугольников, до прямоугольника с точкой В. Достичь точки В в случаях,

когда встречаются препятствия, такие, как уже существующие межсоединения с

точками С и F, можно, используя различные обходные пути с

прямоугольниками, содержащими разные числа. Маршрут, конечный

прямоугольник которого имеет в точке В наименьшее число, является

наикратчайшим путем между точками А и В.

Рисунок 7.1 Метод поиска по лабиринту.

Этим методом, который также называется алгоритмом Ли, всегда можно найти

наикратчайший путь, если он существует. Однако если плата имеет большую

площадь, то требуются большой объем памяти и большие затраты машинного

времени. (Например, если каждая сторона кристалла имеет длину около 6,25 мм,

а сторона квадрата имеет длину 5 мкм, то в таком кристалле содержится более чем

один миллион квадратов.) Поэтому этот алгоритм используется обычно совместно

с другими методами.

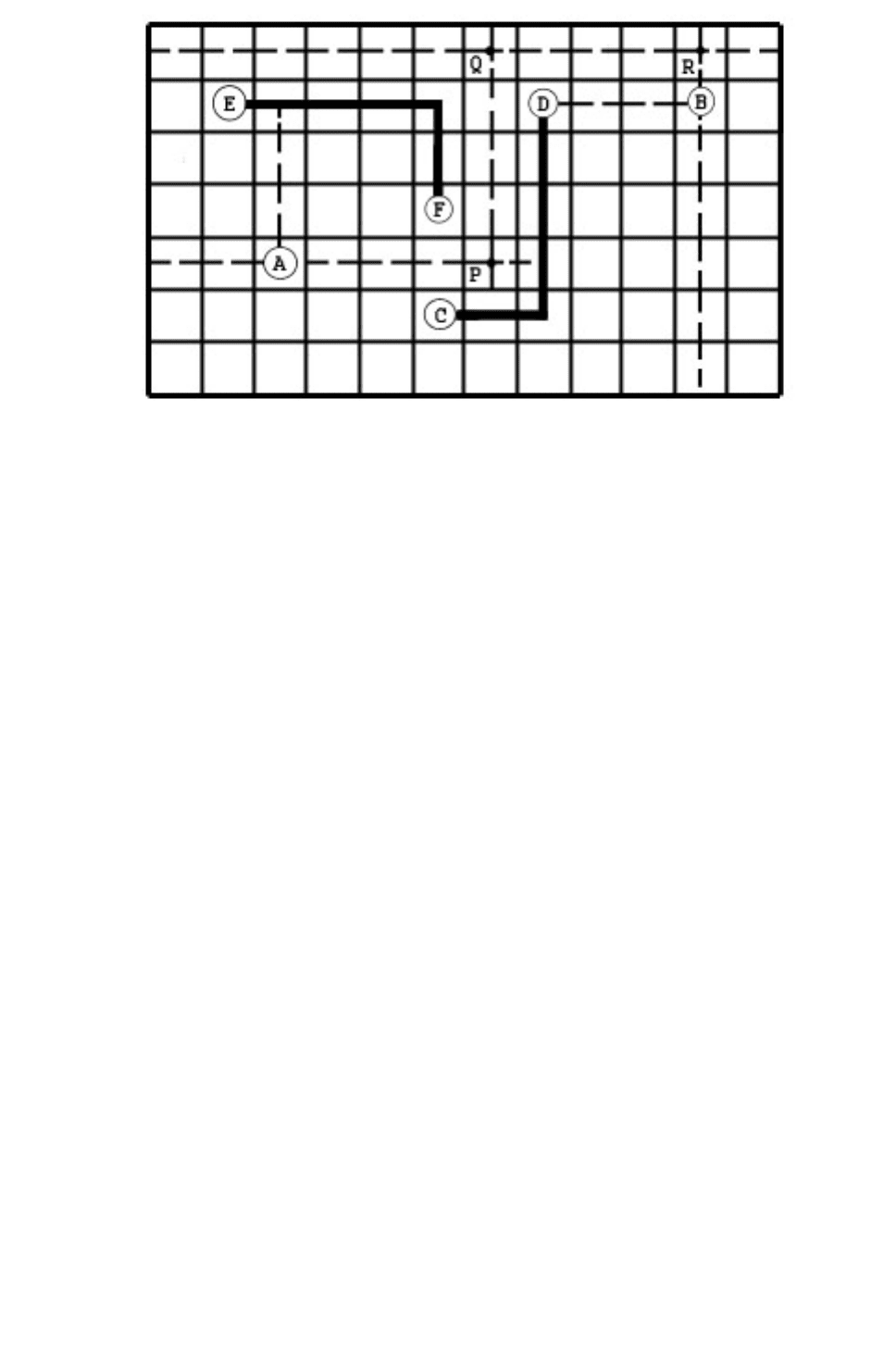

Процедура 7. 1.2.2 Линейный метод поиска

Предположим, что требуется соединить две точки А и В, как показано на

рисунке 7.2. Через точку А проведем вертикальную и горизонтальную штриховые

линии, концы которых ограничиваются либо существующими сплошными линиями,

либо границами кристалла. Затем рисуется горизонтальная или вертикальная линия,

которая пересекает уже проведенные линии, но может продолжаться за пределы

этих линий. Например, двигаясь от точки А по горизонтальной линии к точке Р,

можно пытаться проводить вертикальные линии, одна из которых в точке Р

может быть продолжена вверх.

Если при повторении этой процедуры от точек А к В линии с обеих сторон

встретятся, то получится соединение, такое, как А—P—Q—В (рис. 8.5.2).

Полученное соединение необязательно является самым коротким.

153

Рисунок 7.2 Линейный метод поиска.

При использовании этого метода, когда соединение может быть найдено,

требуется небольшая память и малые затраты машинного времени (хотя процедура

поиска соединения может повторяться много раз). Обычно лишь незначительный

процент соединений требуется позднее выполнять вручную. Однако при очень

большом количестве соединений ручная трассировка даже небольшого процента

соединений может занять очень много времени; для этих целей предложен

специальный аппаратный процессор.

7.1.3 Метод частичного и полного проектирования.

7.1.3.1 Метод полного проектирования на заказ.

Метод полного проектирования на заказ с использованием схем с

произвольной логикой позволяет получить устройство с максимальным

быстродействием или минимальными размерами в зависимости от целей

разработки.

По сравнению с другими методами проектирования его реализация требует

наибольших начальных затрат. Логическое проектирование при использовании

схем с произвольной логикой является более трудоемким, чем в других случаях,

например при минимизации ПЛМ за счет получения минимальных форм

переключательных выражений. Однако наибольшие затраты времени, во много раз

превышающие длительность соответствующих этапов в других методах, приходятся

на этап разработки топологических схем, так как должна быть обеспечена

максимально возможная степень компоновки устройств, причем выполнение этого

этапа производится вручную. Достигаемая при этом плотность компоновки

устройств и межсоединений настолько высока, что исправление допущенных ошибок

чрезвычайно затруднено и требует значительного времени. Если оказывается, что в

топологической схеме по ошибке пропущено одно устройство, разработчики могут

испытать немалые трудности при включении его в ИС. Кроме того, произвольный

характер топологии устройств и межсоединений в ИС обусловливает

154

необходимость больших затрат времени на проверку проекта. При

проектировании, например, БИС с 3 тыс. вентилей разработчику топологических

схем приходится оперировать 300 тыс. прямоугольников на кристалл, если

считать, что один вентиль состоит из 100 прямоугольников. Таким образом, про-

ектирование топологии представляет собой очень сложную задачу, выполнение

которой может осуществляться только с невысокой скоростью, составляющей лишь

5—10 МОП-транзисторов на человека в день с учетом времени, необходимого на вы-

черчивание, проверку и исправление топологической схемы. Таким образом, для

проектирования и разработки топологии БИС, например, содержащей 10 тыс. МОП-

транзисторов, должно быть привлечено по крайней мере несколько человек, а

необходимое время может легко составить 20—40 мес. В таких случаях площадь

всего кристалла разбивается на области, проектирование и разработка топологии

которых производится независимо меньшими группами разработчиков. Начальные

затраты легко могут превысить сумму в 1 млн. долл. С увеличением степени

интеграции затраты резко возрастают.

САПР для минимизации площади ИС может быть использована лишь в очень

незначительной степени, так как глобальная оптимизация, достигаемая за счет

проектирования схем, удовлетворяющих формам и размерам используемых областей

кристалла, может быть лучше выполнена человеком визуальным методом, чем

программой. Однако для выполнения таких работ, как моделирование логики,

проверка топологии и тестирование, САПР находит самое широкое применение.

В действительности все реже встречаются ИС с большой степенью

интеграции, полностью состоящие из схем с произвольной логикой. Доля площади

БИС, занимаемая схемами с произвольной логикой, составляющая 30—40% в

разработках конца 1970 гг. (остальную площадь занимают схемы с регулярной

структурой, т. е. ОЗУ и ПЗУ), будет уменьшаться с переходом к СБИС,

обладающим большей степенью интеграции, для сокращения времени

проектирования топологии. (ОЗУ и ПЗУ совершенно определенно относятся к

схемам с регулярной структурой, хотя четкой границы между схемами с

регулярной структурой и с произвольной логикой, не существует. Несмотря на

то что ПЛМ являются особым типом ПЗУ, они иногда рассматриваются как

схемы с произвольной логикой, хотя по простоте топологии их следует

относить к схемам с регулярной структурой. Схемы с модульной структурой,

построенные на модулях с произвольной логикой, могут быть включены как в

тот, так и в другой класс, но обычно их называют схемами с произвольной

логикой.) Зачастую модульной структурой обладают отдельные части схем с

произвольной логикой, таких, как счетчики и сумматоры с межразрядными

переносами (каскадные одноразрядные сумматоры). Время разработки тополо-

гии для запоминающих устройств может быть в 10—15 раз меньше, чем для

схем с произвольной логикой. Среди последних топология быстрее

разрабатывается для схем, обладающих модульной структурой, так как

топология модулей повторяется. Другое преимущество использования схем с

регулярной структурой заключается в сокращении времени проектирования ло-

гики за счет широкого применения программных средств автоматизации,

например программ минимизации для ПЛМ, или ПЗУ микропрограмм.

Необходимо, однако, подчеркнуть, что даже при расширении степени

155

использования в ИС схем с регулярной структурой схемы с произвольной

логикой сохраняют свое значение для реализации функций, являющихся

критическими по отношению к характеристикам ИС. Таким образом, схемы с

произвольной логикой будут использоваться, по крайней мере частично, в

СБИС, а БИС с невысокой степенью интеграции будут преимущественно или

даже полностью состоять из таких схем.

Метод полного проектирования на заказ позволяет получить наиболее

компактную ИС. При этом ее выпуск в очень больших объемах (порядка 1 млн.

штук и во всяком случае не меньше 100 тыс.) обеспечивает достижение

наименьшей ее стоимости. При небольшом объеме выпуска этот метод

является самым дорогим из-за больших начальных вложений. Компактность

ИС обусловливает возможность получения наилучших характеристик по

быстродействию и потреблению мощности.

7.1.3.2 Методы частичного проектирования на заказ.

В тех случаях, когда метод полного проектирования на заказ требует слишком

больших затрат времени или не оправдан финансовыми соображениями, а

использование серийно выпускаемых ИС ведет к недопустимому увеличению

размеров устройств (а следовательно, и к их удорожанию из-за необходимости

применения дополнительного количества печатных плат или снижению

быстродействия из-за длинных соединений), разумным компромиссом является

метод частичного проектирования на заказ.

В настоящее время при частичном проектировании используют матрицы

вентилей, библиотеки ячеек, а также ряд устройств, включая ПЛМ. Любая

логическая схема может быть спроектирована с использованием только ПЛМ, но

обычно так не делается.

Вентильная матрица представляет собой БИС, в которой в виде матрицы

расположены не соединенные между собой вентили. Строго говоря, в виде

матрицы расположены ячейки, состоящие из несоединенных элементов, а каждая

ячейка при соответствующем соединении этих элементов может реализовать

вентиль одного из нескольких типов. А уже соединением этих вентилей можно

сформировать схему. В результате вместо всех масок, которые необходимо

разработать и изготовить при полном проектировании, требуется специально

спроектировать только 2 или 3. Кроме того, поскольку необходимо разрабатывать

лишь топологию соединений с учетом расположения вентилей, эффективным

оказывается применение САПР, что значительна сокращает затраты времени на

проектирование топологических схем. Таким образом, по сравнению с полным

проектированием на заказ проектирование с использованием матриц вентилей

является очень недорогим и быстрым. Матрицы ЭСЛ- и ТТЛ-вентилей широко

используются в больших системах и мини-ЭВМ.

Матрицы вентилей называют также базовыми пластинами или несвязанными

логическими матрицами.

Вентильные матрицы обладают следующими достоинствами. Даже при

изменении технологии производства или электрической схемы только одна типовая

ячейка устройства (или несколько функционально разных ячеек) нуждаются в

156

157

тщательном проектировании, включая разработку их топологических схем, после

чего эта топология может быть многократно повторена на кристалле. После

проектирования схемы на логических вентилях (хотя на выполнение этой задачи и

требуется много времени, причем основной заботой разработчика будет миними-

зация числа вентилей в условиях ограничений, например, на максимальное

значение коэффициента разветвления по выходу, в то время как проектирование

соединений является проблемой менее значительной) программы САПР

автоматически производят размещение логических вентилей и прокладку

соединений на кристалле, хотя в некоторых сложных случаях размещение,

представляющее большую трудность, нежели маршрутизация должно

выполняться разработчиками вручную, возможно, с использованием вариантов

размещения вентилей из библиотеки стандартных схем. (Как правило, несколько

процентов соединений также не могут быть обработаны программами САПР и

должны быть проложены вручную. Следовательно, когда соединений очень много,

даже несколько процентов составляет большое число соединений. Поэтому очень

важным является сокращение доли таких соединений). Необходимо отметить, что

благодаря заранее определенному положению вентилей в матрице программы

САПР, осуществляющие размещение вентилей и прокладку соединений,

упрощаются. По изложенным выше причинам время проектирования

топологических схем сильно сокращается, что ведет к сокращению общего времени

проектирования, а следовательно, и расходов на проектирование. (Фирмы-

поставщики обычно затрачивают на эту работу от нескольких до десятка недель.)

В каждом конкретном случае требуется разработать на заказ лишь несколько

масок для соединений и контактов, а все остальные маски являются общими для

всех устройств, что позволяет распределить начальные затраты на изготовление

всех этих общих масок на все разрабатываемые устройства. В результате

матрицы вентилей остаются экономически эффективными при таком низком уровне

выпуска, как сотни и тысячи изделий. (При разработке 32-разрядной ЭВМ VAX-

11/780 время проектирования и стоимость за счет использования матриц вентилей

были уменьшены на 15% по сравнению с тем, что могло быть получено при ме-

тоде полного проектирования, и лишь 5 из 13 масок потребовалось разработать

специально.) Быстродействие таких схем выше, чем при их реализации на

дискретных компонентах, МИС или СИС, так как в среднем длина межсоедине-

ний между вентилями уменьшается (большинство межсоединений располагается

внутри кристаллов, а не на печатной плате). В некоторых схемах, которые, как

предполагается, будут часто меняться в ходе проектирования, соединения между

вентилями могут быть выполнены вне кристалла (т. е. расположенные внутри

кристалла вентили используются как дискретные компоненты), хотя это и ведет к

снижению быстродействия и увеличению числа неиспользованных вентилей.

Уменьшается также и потребляемая мощность.

К недостаткам вентильных матриц в первую очередь необходимо отнести

большие размеры кристалла, в котором должно быть отведено много места на

соединения в пределах пар соседних столбцов и строк вентилей. Другим

недостатком является возможность получения высокого процента неиспользован-

ных вентилей, обусловленная следующими причинами. Для некоторых типов

схем или частей большой схемы, размещаемых на матрице вентилей, может

158

оказаться, что занято все пространство, отведенное под соединения (с

применением обходных путей, если кратчайшие заняты другими

соединениями), или все выводы ИС заняты входящими и выходящими

соединениями. В любом случае многие вентили могут быть не использованы

вовсе, а в некоторых случаях доля неиспользованных вентилей может превышать

50%. Из-за этих недостатков ИС средних размеров, построенная на матрице

вентилей, в 4—5 раз больше ИС, полученной при полном проектировании, а для

некоторых схем это соотношение является еще большим. Повышение стоимости

при одинаковых объемах производства будет еще большим (стоимость не

обязательно линейно зависит от размеров ИС). К недостаткам вентильных

матриц относится также сложность обеспечения одинаковых вентильных

задержек. (Если времена задержек вентилей не одинаковы, возникает возмож-

ность появления в схеме ложных сигналов). При полном проектировании

увеличение вентильной задержки за счет большой длины или большого

количества выходных соединений вентиля может быть скомпенсировано

изменением проекта транзисторной схемы. Однако такая точная регулировка

невозможна при использовании матриц вентилей.

В соответствии с разнообразием потребностей пользователей по

быстродействию, потребляемой мощности, стоимости, времени

проектирования, легкости внесения изменений и другим характеристикам схем

фирмы — изготовители полупроводников выпускают большое количество самых

различных матриц вентилей, широко используемых при внутренних

разработках фирмами — изготовителями ЭВМ. На кристаллы помещаются

различные количества вентилей, обладающие различными возможностями по

образованию той или иной конфигурации, принадлежащие к разным типам ИС.

Широко доступны матрицы не только на ТТЛ-вентилях, но и на вентилях типов

ЭСЛ, ТРЛ, И

2

Л, n-МОП, КМОП и КМОПСП, обладающих различными ло-

гическими возможностями. Поскольку возможности матриц вентилей сильно

зависят от их топологии, различные изготовители по-разному располагают

компоненты матриц, придавая тем самым своим изделиям своеобразные

особенности.

7.2 Этапы проектирования СБИС.

7.2.1 Анализ и моделирование электрических схем.

Программные продукты.

Логические схемы должны быть преобразованы в принципиальные

электрические схемы. Когда проектировщики определяют характеристики

электрической схемы (например, быстродействие, номинал напряжения питания,

типы логических операций и допустимые отклонения уровней сигнала)

желательна иметь машинные программы, которые автоматически с учетом всех

159

требований составляют электрические схемы и определяют такие параметры, как

характеристики транзисторов и величины токов. Это весьма непросто. На практике

разработка принципиальных электрических схем происходит следующим обра-

зом. Проектировщики разрабатывают электрические схемы, лишь

приблизительно задавая величины некоторых схемных параметров, затем

анализируют эти схемы при помощи программ автоматизированного

проектирования и затем на основе результатов анализа вносят в схемы изменения.

После того как в результате формирования топологии получены конкретные ве-

личины схемных параметров, проектировщики заканчивают разработку

электрических схем, моделируя и анализируя принципиальные схемы при помощи

прикладных программ. (Эта последовательность действий часто является

итеративной.)

Для моделирования и анализа электрических схем программы

автоматизированного проектирования реализуют численное решение нелинейных

дифференциальных уравнений, описывающих эти схемы. Поскольку расчеты

необходимо закончить в приемлемые сроки, сохранив при этом требуемую точность,

применяются наиболее совершенные методы численного анализа. Программы

автоматизированного проектирования обычно производят анализ переходных

процессов, установившихся постоянных и переменных токов, влияния изменений

температуры, степени искажения сигналов, помехоустойчивости и чувствитель-

ности, выполняют оптимизацию параметров электронных схем.

За период 1964—1972 гг. для анализа электронных схем малой и средней

степени интеграции были разработаны машинные программы, такие, как ТАР,

ЕСАР (фирма IBM) и NET1. Начиная с 1973 г. были разработаны более мощные

программы анализа электрических схем с большой степенью интеграции, такие,

как ASTAP (фирма IBM) и SPICE. В настоящее время в распоряжении

разработчиков имеется много прикладных программ с различными

характеристиками, например CIRCUS 2, SPICE 2, ISPICE, ITAP, NET II,

SUPER*SCEPTRE и UCCAP. Как правило, большинство этих программ могут

оперировать со схемами, состоящими из нескольких сотен транзисторов. В

частности, широко используются в промышленности программа SPICE 2 и ее

модификации.

БИС и СБИС, реализованные на основе МОП-структур, могут содержать

гораздо большее число транзисторов, в связи с чем программы, о которых

упоминалось выше, не в состоянии достаточно быстро их анализировать.

Поэтому в 1975 г. фирма Bell Labs разработала программу MOTIS. Последняя,

благодаря использованию ускоренных методов анализа может быстро выполнять

анализ электронных схем, выполняемых по МОП-технологии, хотя и за счет

уменьшения точности. Программа MOTIS может оперировать со схемами,

содержащими до 1000 МОП-вентилей, а ее вариант MOTIS-C — со схемами,

число МОП-ячеек в которых достигает 2500. При этом следует подчеркнуть,

что, хотя применение этих двух программ ограничивается анализом

переходных характеристик МОП-схем, их быстродействие увеличилось на два

порядка, а число элементов в электронных схемах, которые могут

анализироваться ими, возросло на порядок по сравнению с программами

автоматизированного проектирования, упомянутыми выше. Программа

160

MOSTAP, аналогичная программе MOTIS, может выполнять также и

логическое моделирование.

Примечание. Программы автоматизированного проектирования для анализа

работы транзистора или схемы из нескольких транзисторов очень важны, когда

необходимо внедрять новые производственные методы или новые приборы.

Разработка таких программ моделирования элементов требует от разработчика

глубоких знаний в области физики твердого тела и численных методов анализа.

При логическом проектировании или при проектировании электрических схем

эти знания не нужны, поскольку к этим этапам проектирования ИС уже

определены используемые технологические методы и параметры компонентов.

Поэтому такие программы в этой книге не рассматриваются подробно.

Разработка новых видов памяти с улучшенными характеристиками по существу

сводится к исследованию перспективных направлений технологии и новых типов

компонентов; поэтому в данном случае такие программы совершенно

необходимы.

Программы моделирования полупроводниковых элементов служат для выбора

физической структуры элементов (или транзисторов) с тем, чтобы обеспечить

приемлемый выход годных при изготовлении ИС на этих элементах. На основе

математических моделей элементов, характеризующих физическое поведение

носителей токов и распределение потенциалов, составляются и решаются

нелинейные уравнения в частных производных. Вследствие сложности задачи,

требующей для решения больших затрат машинного времени даже при

использовании лучших численных методов анализа, можно рассчитать структу-

ры, содержащие не больше, чем несколько элементов. К настоящему времени

разработаны такие программы моделирования элементов, как CADDET, MINI-

MOS, GEMINI, DTRAN, SITCAP, MODMAG и TRANS 2D. Поскольку рабочие

характеристики полупроводниковых элементов ИС зависят от используемых при

производстве ИС технологических методов, то необходимы также и программы

моделирования технологических процессов. Для этого были разработаны такие

программы, как SUPREM-II.

7.2.2 Автоматизированное проектирование.

Ранее были рассмотрены только программы автоматизации основных этапов

системного проектирования БИС/СБИС. Однако множество таких программ было

разработано и для автоматизации других аспектов системного проектирования.

Следует уяснить, что автоматизированное проектирование может быть или очень

эффективным, или неэффективным в зависимости от того, где и как оно

применяется. Для повторяющихся простых задач проектирования, таких, как

логическое моделирование, использование программ автоматизации очень

эффективно. При этом решение задачи получается без ошибок и значительно бы-

стрее, чем если бы оно искалось разработчиками вручную. Для таких сложных

задач, как функциональное проектирование, использование ЭВМ не дает

существенных результатов (хотя если функциональное проектирование уже

завершено, то моделирование с помощью прикладных программ является эффек-

тивным). К тому же для некоторых задач подготовка исходных данных для