Neamen D. Microelectronics: Circuit Analysis and Design

Подождите немного. Документ загружается.

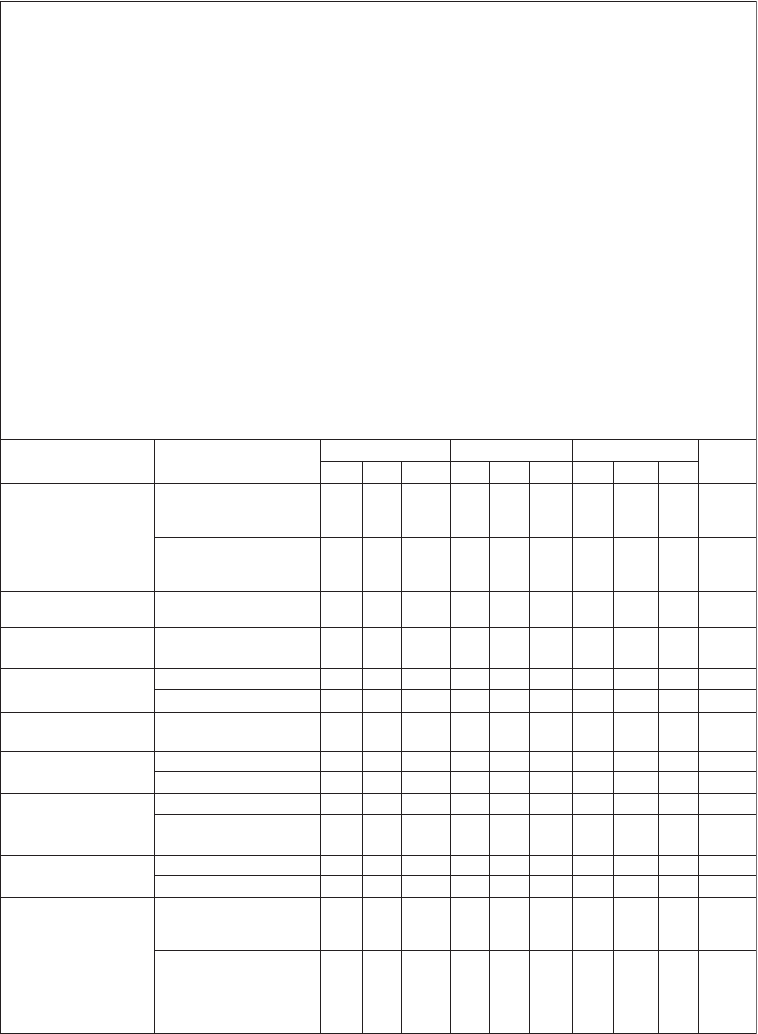

1318 Appendix B Selected Manufacturers’ Data Sheets

National

Semiconductor

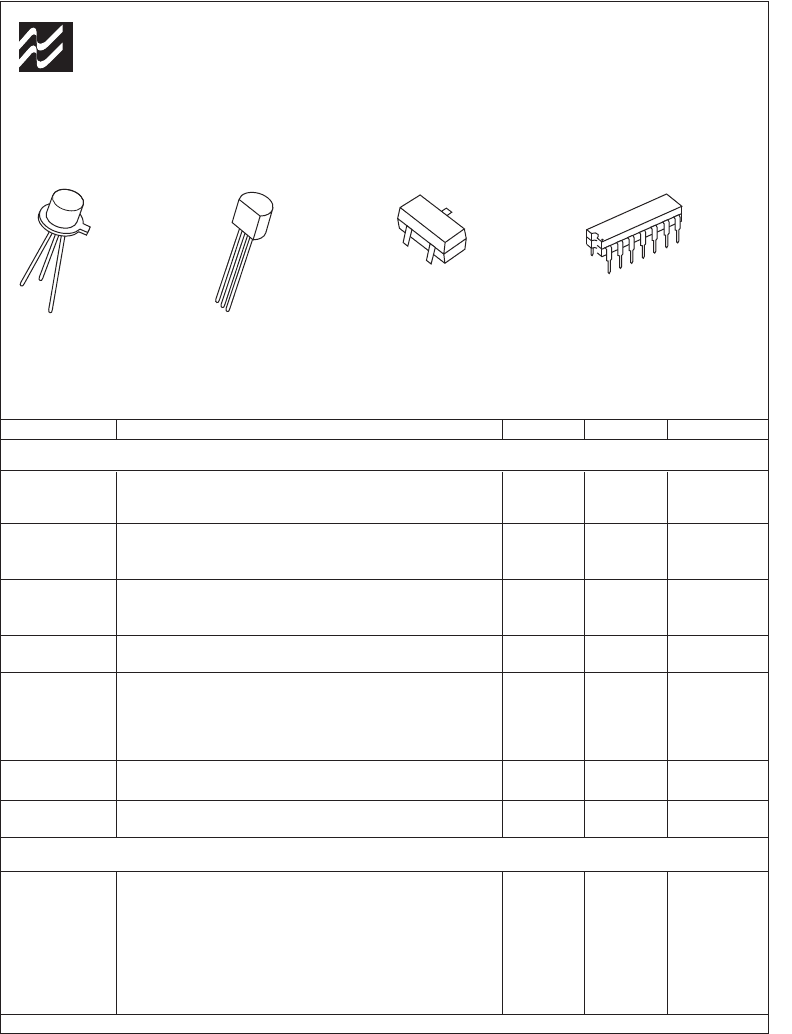

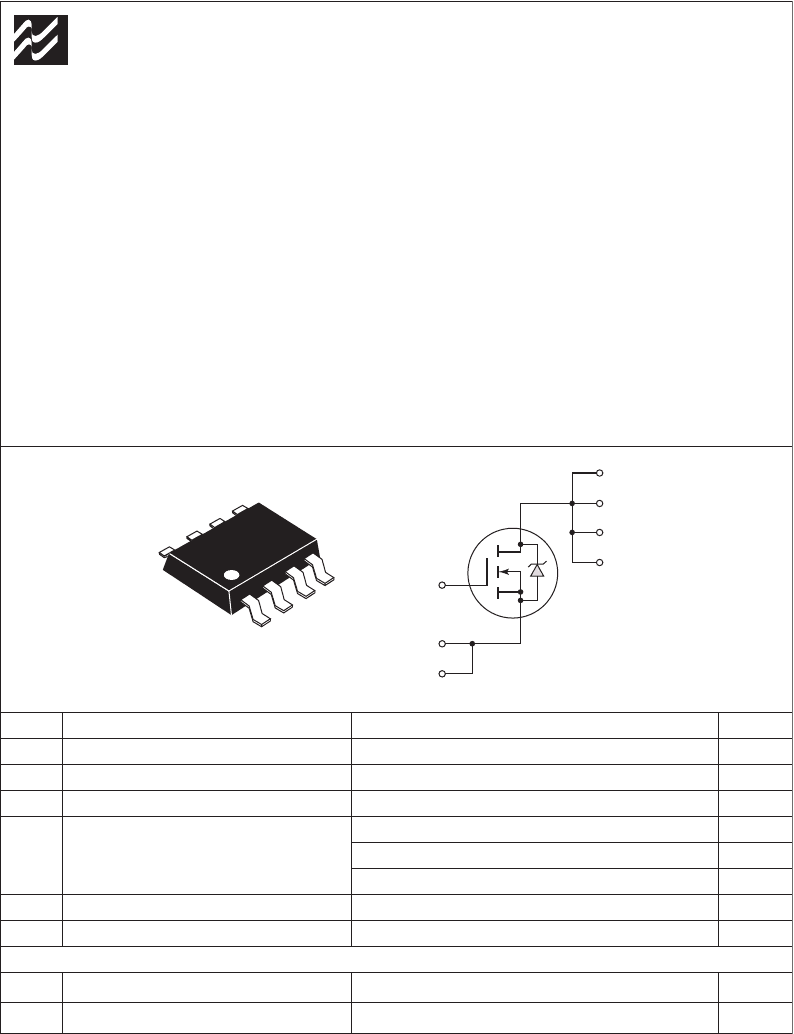

2N2222

2N2222A

PN2222

PN2222A

MMBT2222

MMBT2222A

MPQ2222

TO–18 TO–92 TO–236

(SOT–23)

TO –116

C

C

C

C

B

B

B

B

E

E

E

E

14

1

NPN General Purpose Amplifier

Electrical Characteristics

T

A

= 25 °C unless otherwise noted

Parameter

Symbol

OFF CHARACTERISTICS

Min Max Units

Collector-Emitter Breakdown Voltage (Note 1)

(

I

C

= 10 mA, I

B

= 0)

Collector-Base Breakdown Voltage

(I

C

= 10 mA, I

E

= 0)

Emitter Base Breakdown Voltage

(

I

E

= 10 mA, I

C

= 0)

2222

2222A

2222

2222A

2222

2222A

2222A

2222A

2222A

222

2222A

2222

2222A

2222

2222A

Collector Cutoff Current

(

V

CE

= 60 V,

V

EB(OFF)

= 3.0 V)

Collector Cutoff Current

(V

CB

= 50 V,

I

E

= 0)

(

V

CB

= 60 V, I

E

= 0)

(

V

CB

= 50 V, I

E

= 0, T

A

= 150 °C)

(

V

CB

= 60 V, I

E

= 0, T

A

= 150 °C)

Emitter Cutoff Current

(

V

EB

= 3.0 V, I

C

= 0)

Base Cutoff Current

(V

CE

= 60 V, V

EB(OFF)

= 3.0)

DC Current Gain

(

I

C

= 0.1 mA, V

CE

= 10 V)

(

I

C

= 1.0 mA, V

CE

= 10 V)

(

I

C

= 10 mA, V

CE

= 10 V)

(

I

C

= 10 mA, V

CE

= 10 V, T

A

= –55 °C)

(

I

C

= 150 mA, V

CE

= 10 V) (Note 1)

(

I

C

= 150 mA, V

CE

= 1.0 V) (Note 1)

(

I

C

= 500 mA, V

CE

= 10 V) (Note 1)

Note 1: Pulse Test: Pulse Width ≤ 300 m s, Duty Cycle ≤ 2.0%.

ON CHARACTERISTICS

35

50

75

35

100

50

30

40

300

20

10

0.01

0.01

10

10

mA

nA

nA

nA

30

40

60

75

5.0

6.0

V

V

V

10

2N2222/PN2222/MMBT2222/MPQ2222/2N2222A/PN2222A/MMBT2222A NPN General Purpose Amplifier

V

(BR)CEO

V

(BR)CBO

V

(BR)EBO

I

CEX

I

CBO

I

EBO

I

BL

h

FE

nea80644_appB_1317-1328.qxd 8/6/09 10:07 AM Page 1318 pmath DATA-DISK:Desktop Folder:UDAYVEER/Neamen:

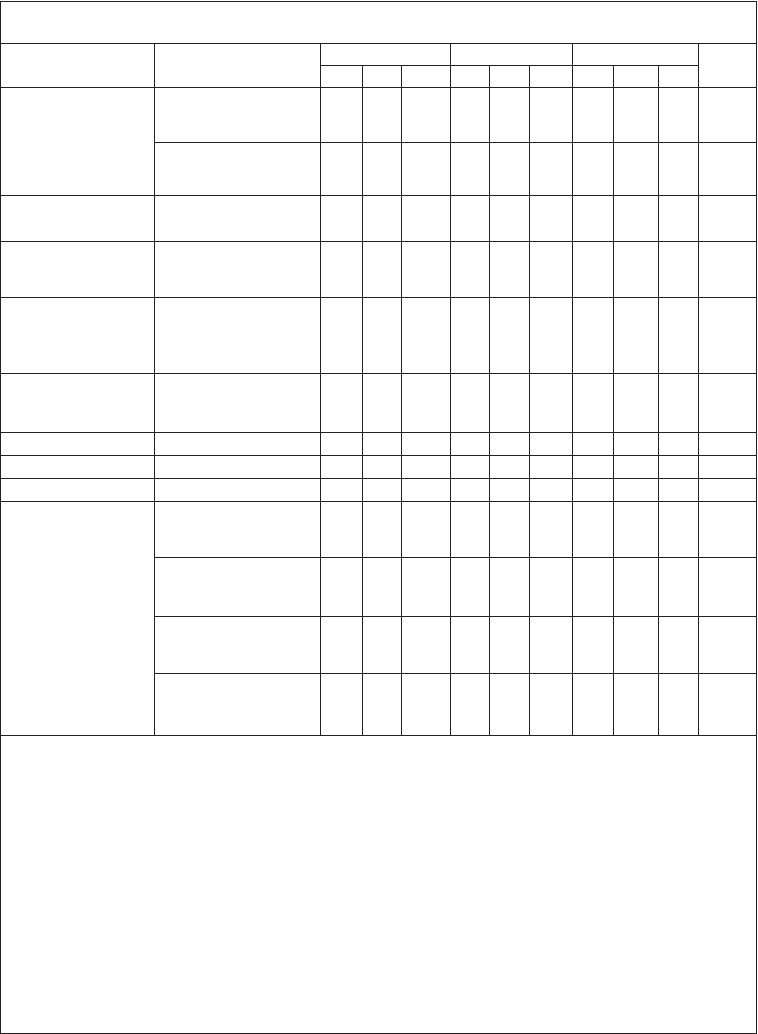

Appendix B Selected Manufacturers’ Data Sheets 1319

2222

2222A

Note 1: Pulse Test: Pulse Width <300 m s, Duty Cycle ≤ 2.0%.

Note 2: For characteristics curves, see Process 19.

Note 3: f

T

is defined as the frequency at which h

fe

extrapolates to unity.

NPN General Purpose Amplifier (Continued )

Electrical Characteristics

T

A

= 25 °C unless otherwise noted (Continued )

Parameter

Symbol

ON CHARACTERISTICS (Continued )

Min Max Units

Collector-Emitter Saturation Voltage (Note 1)

(

I

C

= 150 mA, I

B

= 15 mA)

(

I

C

= 500 mA, I

B

= 50 mA)

Base-Emitter Saturation Voltage (Note 1)

(

I

C

= 150 mA, I

B

= 15 mA)

(

I

C

= 500 mA, I

B

= 50 mA)

2222A

2222A

2222

2222A

2222

2222A

2222

2222A

2222

2222A

2222

2222A

ns

ns

ns

ns

V

CE

(sat)

V

BE

(sat)

SMALL-SIGNAL CHARACTERISTICS

Real Part of Common-Emitter

High Frequency Input Impedance

(

I

C

= 20 mA, V

CE

= 20 V, f = 300 MHz)

Noise Figure

(

I

C

= 100 mA, V

CE

= 10 V, R

S

= 1.0 kΩ, f = 1.0 kHz)

Collector Base Time Constant

(

I

E

= 20 mA, V

CB

= 20 V, f = 31.8 MHz)

Input Capacitance (Note 3)

(V

EB

= 0.5 V, I

C

= 0, f = 100 kHz)

Output Capacitance (Note 3)

(

V

CB

= 10 V, I

E

= 0, f = 100 kHz)

Current Gain—Bandwidth Product (Note 3)

(I

C

= 20 mA, V

CE

= 20 V, f = 100 MHz)

SWITCHING CHARACTERISTICS

Delay Time

Rise Time

Storage Time

Fall Time

(

V

CC

= 30 V,

V

BE

(OFF)

= 0.5 V,

I

C

= 150 mA, I

B1

= 15 mA)

(

V

CC

= 30 V, I

C

= 150 mA,

I

B1

= I

B2

= 15 mA)

except

MPQ2222

except

MPQ2222

10

25

225

60

60

Ω

4.0

dB

150

ps

30

25

pF

8.0

pF

250

300

MHz

V

V

0.6

0.6

1.3

1.2

2.6

2.0

0.4

0.3

1.6

1.0

Re(h

ie

)

2222/PN2222/MMBT2222/MPQ2222/2N2222A/PN2222A/MMBT2222A NPN General Purpose Amplifier

f

T

C

obo

C

ibo

rb'C

C

NF

t

D

t

R

t

S

t

F

nea80644_appB_1317-1328.qxd 8/6/09 10:07 AM Page 1319 pmath DATA-DISK:Desktop Folder:UDAYVEER/Neamen:

1320 Appendix B Selected Manufacturers’ Data Sheets

National

Semiconductor

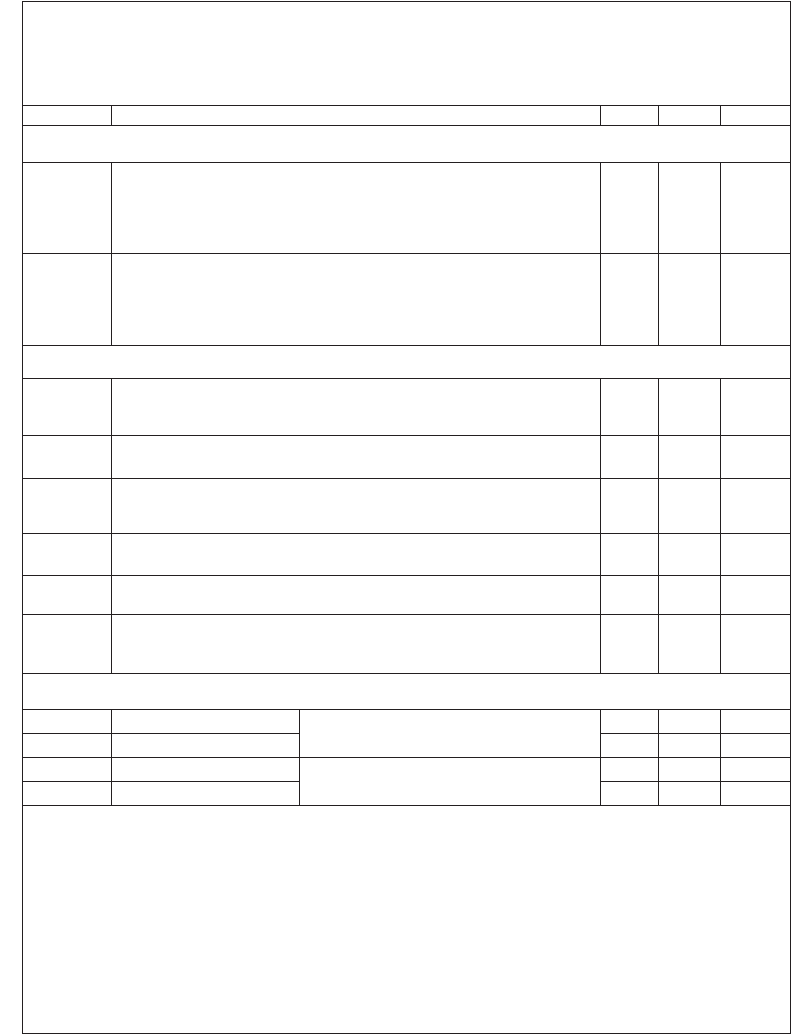

2N2907

2N2907A

PN2907

PN2907A

MMBT2907

MMBT2907A

MPQ2907

TO–18 TO–92 TO–236

(SOT–23)

TO –116

C

C

C

C

B

B

B

B

E

E

E

E

14

1

PNP General Purpose Amplifier

Electrical Characteristics

T

A

= 25 °C unless otherwise noted

Parameter

Symbol

OFF CHARACTERISTICS

Min Max Units

Collector-Emitter Breakdown Voltage (Note 1)

(

I

C

= 10 mAdc, I

B

= 0)

Collector-Base Breakdown Voltage

(I

C

= 10 m Adc, I

E

= 0)

Emitter Base Breakdown Voltage

(

I

E

= 10 m Adc, I

C

= 0)

2907

2907A

2907

2907A

2907

2907A

I

B

Collector Cutoff Current

(V

CE

= 30 Vdc,

V

BE

= 0.5 Vdc)

Collector Cutoff Current

(V

CB

= 50 Vdc,

I

E

= 0)

(

V

CB

= 50 Vdc, I

E

= 0, T

A

= 150 °C)

Base Cutoff Current

(V

CE

= 30 Vdc, V

EB

= 0.5 Vdc)

50

0.020

0.010

20

10

mAdc

nAdc

nAdc

40

60

60

5.0

Vdc

Vdc

Vdc

50

2N2907/PN2907/MMBT2907/MPQ2907/2N2907A/PN2907A/MMBT2907A PNP General Purpose Amplifier

V

(

BR)CEO

V

(

BR)CBO

V

(

BR)EBO

I

CEX

I

CBO

nea80644_appB_1317-1328.qxd 8/6/09 10:07 AM Page 1320 pmath DATA-DISK:Desktop Folder:UDAYVEER/Neamen:

Appendix B Selected Manufacturers’ Data Sheets 1321

Note 1: Pulse Test: Pulse Width ≤ 300 m s, Duty Cycle ≤ 2.0%.

PNP General Purpose Amplifier (Continued )

Electrical Characteristics

T

A

= 25 °C unless otherwise noted (Continued )

Parameter

Symbol

ON CHARACTERISTICS

Min Max Units

DC Current Gain

(

I

C

= 0.1 mAdc, V

CE

= 10 Vdc)

(

I

C

= 1.0 mAdc, V

CE

= 10 Vdc)

(

I

C

= 10 mAdc, V

CE

= 10 Vdc)

(I

C

= 150 mAdc, V

CE

= 10 Vdc) (Note 1)

(

I

C

= 500 mAdc, V

CE

= 10 Vdc) (Note 1)

Collector-Emitter Saturation Voltage (Note 1)

(I

C

= 150 mAdc, I

B

= 15 mAdc)

(

I

C

= 500 mAdc, I

B

= 50 mAdc)

2907

2907A

2907

2907A

2907

2907A

2907

2907A

35

75

50

100

75

100

100

30

50

300

0.4

1.6

Vdc

Vdc

1.3

2.6

ns

ns

h

FE

V

CE

(sat)

Base-Emitter Saturation Voltage

(

I

C

= 150 mAdc, I

B

= 15 mAdc) (Note 1)

(

I

C

= 150 mAdc, I

B

= 50 mAdc)

V

BE (sat)

SMALL-SIGNAL CHARACTERISTICS

Input Capacitance

(

V

EB

= 2.0 Vdc, I

C

= 0, f = 100 kHz)

Output Capacitance

(

V

CB

= 10 Vdc, I

E

= 0, f = 100 kHz)

Current Gain—Bandwidth Product

(

I

C

= 50 mAdc, V

CE

= 20 Vdc, f = 100 MHz)

SWITCHING CHARACTERISTICS

Delay Time

Rise Time

ns

ns

ns

Turn-Off Time

Storage Time

Fall Time

(

V

CC

= 30 Vdc,

I

C

= 150 mAdc,

I

B1

= 15 mAdc)

(

V

CC

= 6.0 Vdc,

I

C

= 150 mAdc,

I

B1

= I

B2

= 15 mAdc)

Except

MPQ2907

Except

MPQ2907

10

ns

Turn-On Timet

on

t

off

45

40

100

80

30

pF

pF

30

MHz

8.0

200

2N2907/PN2907/MMBT2907/MPQ2907/2N2907A/PN2907A/MMBT2907A PNP General Purpose Amplifier

f

T

C

obo

C

ibo

t

d

t

r

t

s

t

f

nea80644_appB_1317-1328.qxd 8/6/09 10:07 AM Page 1321 pmath DATA-DISK:Desktop Folder:UDAYVEER/Neamen:

1322 Appendix B Selected Manufacturers’ Data Sheets

D

D

D

D

D

D

D

D

G

G

S

S

S

S

NC

8-SOIC

NDS9410

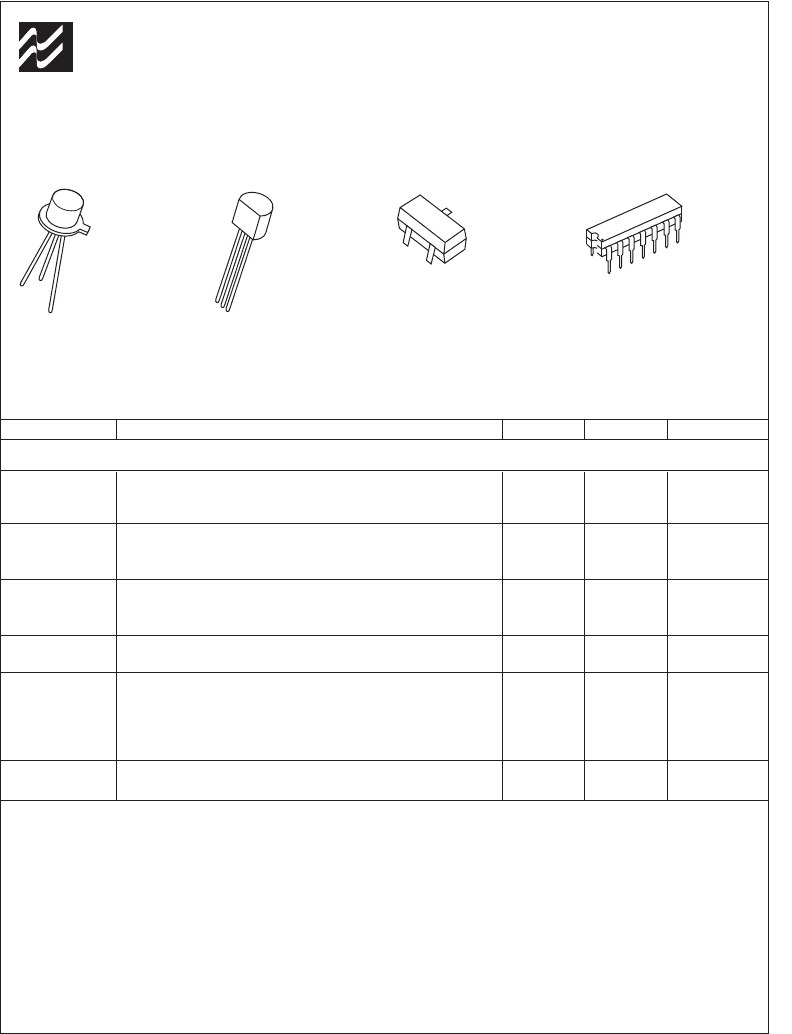

Single N-Channel Enhancement Mode Field Effect Transistor

General Description Features

These N-channel enhancement mode power field

effect transistors are produced using National’s

proprietary, high cell density, DMOS technology.

This very high density process has been especially

tailored to minimize on-state resistance, provide

superior switching performance, and withstand high

energy pulses in the avalanche and commutation

modes. These devices are particularly suited to low

voltage applications such as laptop computer power

management and other battery powered circuits

where fast switching, low in-line power loss, and

resistance to transients are needed.

• 7.0 A, 30 V. R

DS(ON)

= 0.03 Ω

• Rugged internal source-drain diode can eliminate

the need for an external Zener diode transient

suppressor

• High density cell design (3.8 million/in

2

) for

extremely low R

DS(ON)

• High power and current handling capability in a

widely used surface mount package

• Critical DC electrical parameters specified at

elevated temperature

ABSOLUTE MAXIMUM RATINGS T

C

= 25

°

C unless otherwise noted

Symbol Parameter NDS9410

Units

V

DSS

Drain-Source Voltage

V

DGR

Drain-Gate Voltage (R

GS

≤ 1 MΩ)

V

GSS

Gate-Source Voltage

I

D

Drain Current – Continuous @ T

A

= 25 °C

–

– Pulsed

P

D

Maximum Power Dissipation @ T

A

= 25 °C

T

j

T

STG

Operating and Storage Temperature Range

THERMAL CHARACTERISTICS

R

qJA

(t )

R

qJA

Thermal Resistance, Junction-to-Ambient

(Pulse = 10 seconds)

Thermal Resistance, Junction-to-Ambient

(Steady-State)

30

30

±20

±7.0

±5.8

±20

V

V

V

A

A

A

W

°C

°C/W

°C/W

–55 to 150

2.5 (Note 1)

50

(Note 1)

100 (Note 2)

National

Semiconductor

Continuous @ T

A

= 70 °C

nea80644_appB_1317-1328.qxd 8/6/09 10:07 AM Page 1322 pmath DATA-DISK:Desktop Folder:UDAYVEER/Neamen:

Appendix B Selected Manufacturers’ Data Sheets 1323

Notes:

1. Maximum power dissipation and thermal resistance based on an assumption that a 10 second pulse is equivalent to steady-state and using a single-sided

maximum-copper mounting board.

2. Junction-to-ambient thermal resistance based on steady-state conditions in still air using mounting board with minimum heat dissipation characteristics.

3. Pulse Test: Pulse Width ≤ 300

m

s, Duty Cycle ≤ 2.0%.

ELECTRICAL CHARACTERISTICS (T

C

= 25 °C unless otherwise noted)

Symbol

OFF CHARACTERISTICS

Parameter Conditions

Min Typ Max Units

Gate–Body Leakage, Forward

Gate–Body Leakage, Reverse

BV

DSS

Drain-Source Breakdown

Voltage

V

GS

= 0 V, I

D

= 250 mA

V

GS

= 20 V, V

DS

= 0 V

V

GS

= –20 V, V

DS

= 0 V

V

GS

= 10 V, V

DS

= 5 V

V

GS

= 2.7 V, V

DS

= 2.7 V

V

DS

= 15 V, I

D

= 7.0 V

V

DS

= 15 V, V

GS

= 0 V,

f = 1.0 MHz

V

DD

= 25 V, I

D

= 1 A,

V

GEN

= 10 V, R

GEN

= 6 Ω

V

DS

= 15 V,

I

D

= 2.0 A, V

GS

= 10 V

V

GS

= 0 V, I

S

= 2.0 A (Note 3)

V

GS

= 0 V, I

S

= 2 A, dl

S

/dt = 100 A/ms

V

DS

= VGS,

I

D

= 250 mA

V

GS

= 10 V,

I

D

= 7.0 A

V

GS

= 4.5 V,

I

D

= 3.5 A

V

DS

= 24 V,

V

GS

= 0 V

I

DSS

Zero Gate Voltage Drain

Current

I

GSSF

I

GSSR

R

DS(ON )

I

D(ON)

C

ISS

C

OSS

C

RSS

t

D(ON)

t

r

t

D(OFF)

Q

g

Q

gs

Q

gd

I

S

V

SD

t

rr

t

r

g

FS

V

GS(h)

ON CHARACTERISTICS (Note 3)

DYNAMIC CHARACTERISTICS

SWITCHING CHARACTERISTICS (Note 3)

DRAIN-SOURCE DIODE CHARACTERISTICS AND MAXIMUM RATINGS

30

2

25

100

–100

1.4

V

m

A

Gate Threshold Voltage

Static Drain-Source

On-Resistance

On-State Drain Current

Forward Transconductance

Input Capacitance

Output Capacitance

Reverse Transfer Capacitance

Turn-On Delay Time

Turn-On Rise Time

Turn-Off Delay Time

Turn-Off Fall Time

Total Gate Charge

Gate-Source Charge

Gate-Drain Charge

Maximum Continuous Drain–Source Diode Forward Current

Drain-Source Diode Forward

Voltage

Reverse Recovery Time

m

A

nA

nA

V

1

1

0.7

V

0.022

0.033

0.031

0.045

3

2.2

0.03

0.045

0.05

0.075

20

Ω

Ω

Ω

Ω

A

7.7

A

15

S

1250

pF

610

pF

260

pF

10

ns

30

15

ns

60

70

ns

150

50

ns

140

41

nC

50

A

2.2

0.76

V

1.1

100

ns

2.8

nC

12

nC

T

C

= 125 °C

T

C

= 125 °C

T

C

= 125 °C

T

C

= 125 °C

nea80644_appB_1317-1328.qxd 8/6/09 10:07 AM Page 1323 pmath DATA-DISK:Desktop Folder:UDAYVEER/Neamen:

1324 Appendix B Selected Manufacturers’ Data Sheets

0.6

0.8

1

1.2

1.4

1.6

1.8

–50 –25 0 25 50 75 100 125 150

0.5

0.6

0.7

0.8

0.9

1

1.1

1.2

1.3

–50 –25 0 25 50 75 100 125 150

0.6

0.8

1

0 5 10 15 20

1.2

1.4

1.6

1.8

2

0.02

0.01

0 5 10 15 20

0.04

0.03

0.06

0.05

0

0 0.5 1 1.5 2 2.5 3

5

10

15

20

25

5

0

15

10

1 1.5 2 2.5 3 3.5 4

20

V

DS

, DRAIN-SOURCE VOLTAGE (V)

V

GS

= 10, 6

5, 4.5, 4 V

3.5

3.0

2.5

T

J

, JUNCTION TEMPERATURE (°C)

I

D

= 3.5 A

V

GS

= 4.5 V

V

GS

, GATE-TO-SOURCE VOLTAGE (V)

125

25

V

DS

= 10 V

T

J

= –55 °C

T

J

, JUNCTION TEMPERATURE (°C)

V

DS

= VGS

I

D

= 250 mA

I

D

, DRAIN CURRENT (A)

T

J

= 125 °C

25 °C

–55 °C

V

GS

= 4.5 V

10 V

10 V

4.5 V

10 V

4.5 V

I

D

, DRAIN CURRENT (A)

V

GS

= 3 V

3.5

4.5

10

4.0

5.0

6.0

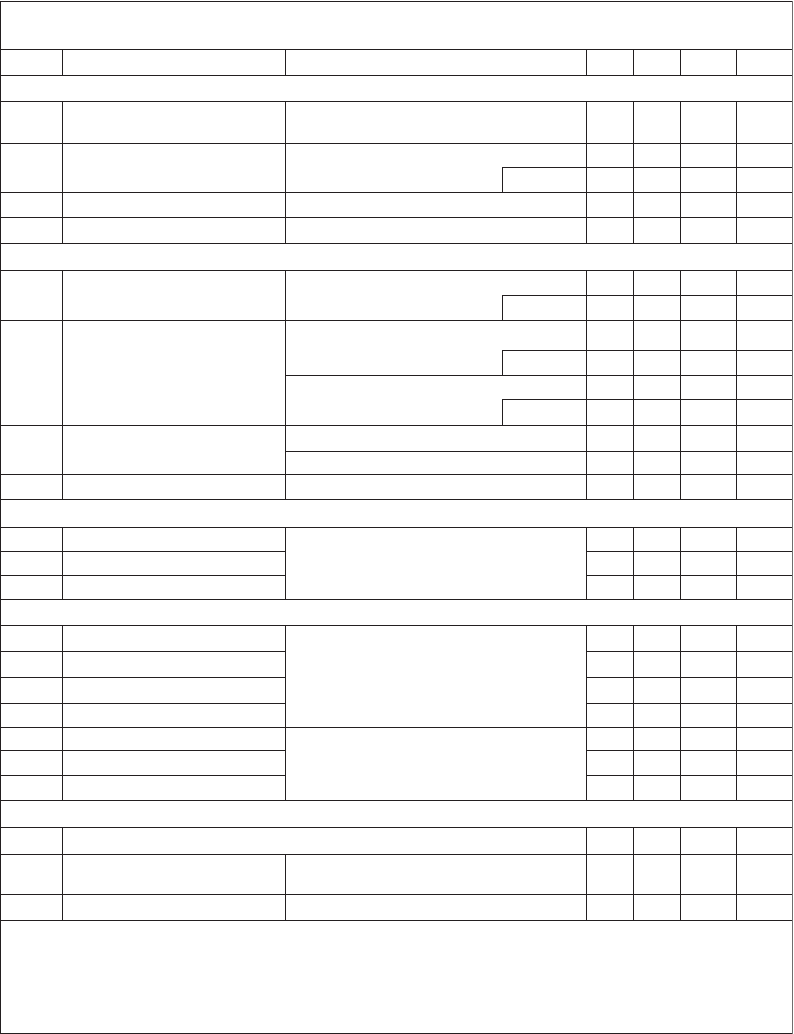

Figure 2. On-Resistance Variation with Drain

Current and Gate Voltage

Figure 1. On-Region Characteristics

Figure 3. On-Resistance Variation with

Temperature

Figure 4. On-Resistance Variation with Drain

Current and Temperature

Figure 6. Gate Threshold Variation with

Temperature

Figure 5. Transfer Characteristics

TYPICAL ELECTRICAL CHARACTERISTICS

I

D

, DRAIN-SOURCE CURRENT (A)

I

D

, DRAIN CURRENT (A)

R

DS(on)

, NORMALIZED

DRAIN-SOURCE ON-RESISTANCE

V

h

, NORMALIZED

GATE-SOURCE THRESHOLD VOLTAGE

R

DS(on)

, NORMALIZED

DRAIN-SOURCE ON-RESISTANCE

R

DS(on)

, ON-RESISTANCE (ohms)

nea80644_appB_1317-1328.qxd 8/6/09 10:07 AM Page 1324 pmath DATA-DISK:Desktop Folder:UDAYVEER/Neamen:

Appendix B Selected Manufacturers’ Data Sheets 1325

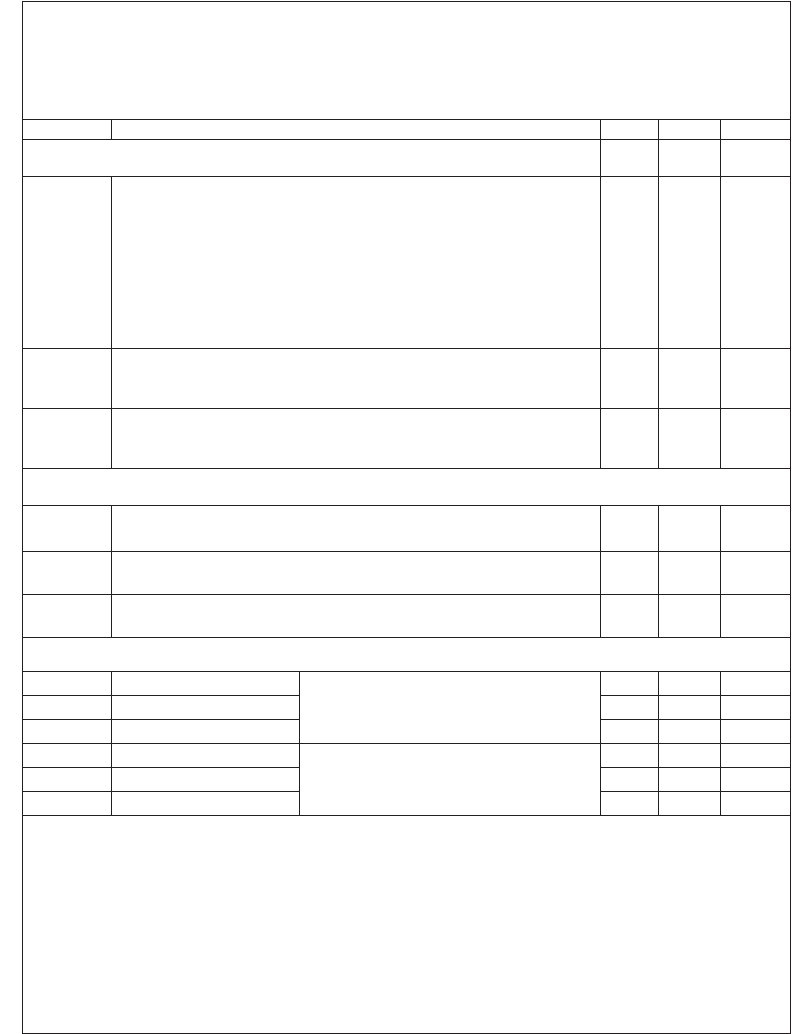

LM741 Operation Amplifier

General Description

The LM741 series are general purpose operational amplifiers

which feature improved performance over industry standards

like the LM709. They are direct, plug-in replacements for the

709C, LM201, MC1439 and 748 in most applications. The

amplifiers offer many features which make their application

nearly foolproof: overload protection on the input and output,

no latch-up when the common mode range is exceeded as well

as freedom from oscillations.

The LM741C/LM741E are identical to the LM741/LM741A

except that the LM741C/LM741E have their performance

guaranteed over a 0 °C to +70 °C temperature range, instead

of –55 °C to +125 °C.

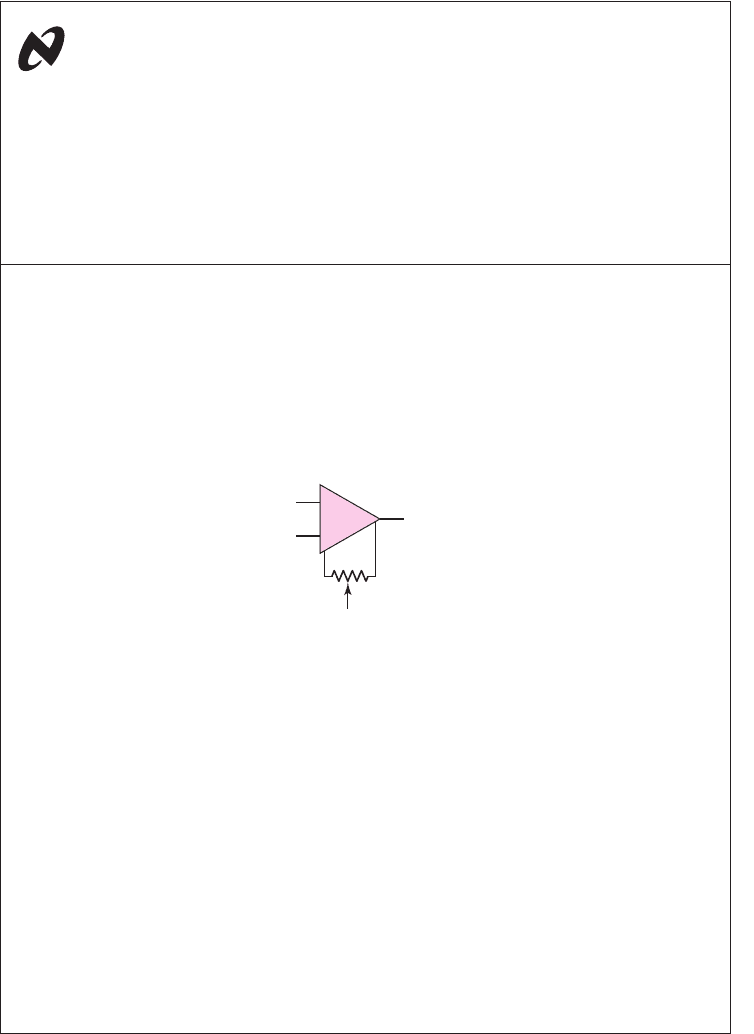

Schematic Diagram – (See Figure 13.3 in text)

10 kΩ

OUTPUT

V

–

Offset Nulling Circuit

LM741 Operational Amplifier

–

+

National Semiconductor

LM741

nea80644_appB_1317-1328.qxd 8/6/09 10:07 AM Page 1325 pmath DATA-DISK:Desktop Folder:UDAYVEER/Neamen:

1326 Appendix B Selected Manufacturers’ Data Sheets

Absolute Maximum Ratings

Supply Voltage

Power Dissipation

Differential Input Voltage

Input Voltage (Note 2)

Output Short Circuit Duration

Operating Temperature Range

Storage Temperature Range

Junction Temperature

LM741A

±22 V

500 mW

±30 V

±15 V

Continuous

–55 °C to +125 °C

–65 °C to +150 °C

150 °C

LM741E

±22 V

500 mW

±30 V

±15 V

Continuous

0 °C to +70 °C

–65 °C to +150 °C

100 °C

LM741

±22 V

500 mW

±30 V

±15 V

Continuous

–55 °C to +125 °C

–65 °C to +150 °C

150 °C

LM741C

±18 V

500 mW

±30 V

±15 V

Continuous

0 °C to +70 °C

–65 °C to +150 °C

100 °C

Electrical Characteristics

Parameter

Conditions

LM741A/LM741E

Min Typ Max Min Typ Max Min Typ Max

LM741

LM741C

Units

Input Offset Voltage T

A

= 25 °C

R

S

≤ 10 kΩ

R

S

≤ 50 Ω

R

L

≥ 2 kΩ

V

S

= ±20 V, V

O

= ±15 V

V

S

= ±15 V, V

O

= ±10 V

V

S

= ±5 V, V

O

= ±2 V

T

A

= 25 °C, R

L

≥ 2 kΩ

V

S

= ±20 V, V

O

= ±15 V

V

S

= ±15 V, V

O

= ±10 V

T

A

= 25 °C, V

S

= ±20 V

T

A

= 25 °C, V

S

= ±20 V

V

S

= ±20 V

T

A

= 25 °C

T

A

= 25 °C

T

A

= 25 °C

T

AMIN

≤ T

A

≤ T

AMAX

R

S

≤ 50 Ω

R

S

≤ 10 kΩ

T

AMIN

≤ T

A

≤ T

AMAX

T

AMIN

≤ T

A

≤ T

AMAX,

T

AMIN

≤ T

A

≤ T

AMAX,

T

AMIN

≤ T

A

≤ T

AMAX

T

AMIN

≤ T

A

≤ T

AMAX

Average Input Offset

Voltage Drift

Input Offset Voltage

Adjustment Range

Input Offset Current

Average Input Offset

Current Drift

Input Bias Current

Input Resistance

Input Voltage Range

Large Signal Voltage

Gain

32

10

25 15

V/mV

V/mV

V/mV

V/mV

V/mV

50

50 200 20 200

±12

±12

±15

±15

±10

±13

±13

V

V

MΩ

MΩ

mA

nA

nA

nA

nA/°C

mV/°C

mV

mV

mV

mV

mV

3.0

0.8

1.0 5.0 2.0 6.0

4.0

6.0

15

3.0 30

70

0.5

20

200 20 200

85 500

300

80

0.210

30 80

500

80

500

0.8

2.0

0.3

1.5

1.0 6.0 0.3 2.0

0.5

7.5

nea80644_appB_1317-1328.qxd 8/6/09 10:07 AM Page 1326 pmath DATA-DISK:Desktop Folder:UDAYVEER/Neamen:

Appendix B Selected Manufacturers’ Data Sheets 1327

Electrical Characteristics (Continued)

Parameter

Conditions

LM741A/LM741E

Min Typ Max Min Typ Max Min Typ Max

LM741

LM741C

Units

Output Voltage Swing V

S

= ±20 V

R

L

≥ 10 kΩ

R

L

≥ 2 kΩ

V

S

= ±15 V

R

L

≥ 10 kΩ

R

L

≥ 2 kΩ

T

A

= 25 °C

T

AMIN

≤ T

A

≤ T

AMAX

T

A

= 25 °C, Unity Gain

T

A

= 25 °C, Unity Gain

T

A

= 25 °C

T

A

= 25 °C

T

A

= 25 °C

V

S

= ±20 V

V

S

= ±15 V

V

S

= ±20 V

T

A

= T

AMIN

T

A

= T

AMAX

V

S

= ±20 V

T

A

= T

AMIN

T

A

= T

AMAX

V

S

= ±15 V

T

A

= T

AMIN

T

A

= T

AMAX

Output Short Circuit

Current

Common-Mode

Rejection Ratio

Supply Voltage Rejection

Ratio

Transient Response

Rise Time

Overshoot

Bandwidth

Slew Rate

Supply Current

Power Consumption

LM741A

LM741E

LM741

165

135

100

75

60

45

150

150

85

mW

mW

mW

mW

mW

mW

mW

mW

85

5050

80 150

±15

±16

mA

V/

ms

V

V

V

V

MHz

dB

dB

dB

dB

mA

mA

10

352510

80

90

25

40

9070

25

70

96

95

86

77

96

77

96

0.3

5555

0.5 0.5

1.7 2.8 1.7 2.8

0.3

20

0.80.25

6.0

0.7

0.3

0.437 1.5

±13

±14

±10

±12

±13

±14

±10

±12

m s

%

Note 2: For supply voltages less than ±15 V, the absolute maximum input voltage is equal to the supply voltage.

T

AMIN

≤ T

A

≤ T

AMAX

R

S

≤ 10 kΩ, V

CM

= ±12 V

R

S

≤ 50 Ω, V

CM

= ± 12 V

T

AMIN

≤ T

A

≤ T

AMAX

V

S

= ±20 V to V

S

= ±5 V

R

S

≤ 50 Ω

R

S

≤ 10 Ω

nea80644_appB_1317-1328.qxd 8/6/09 10:07 AM Page 1327 pmath DATA-DISK:Desktop Folder:UDAYVEER/Neamen: